249

APPENDIX B Bus Operation List

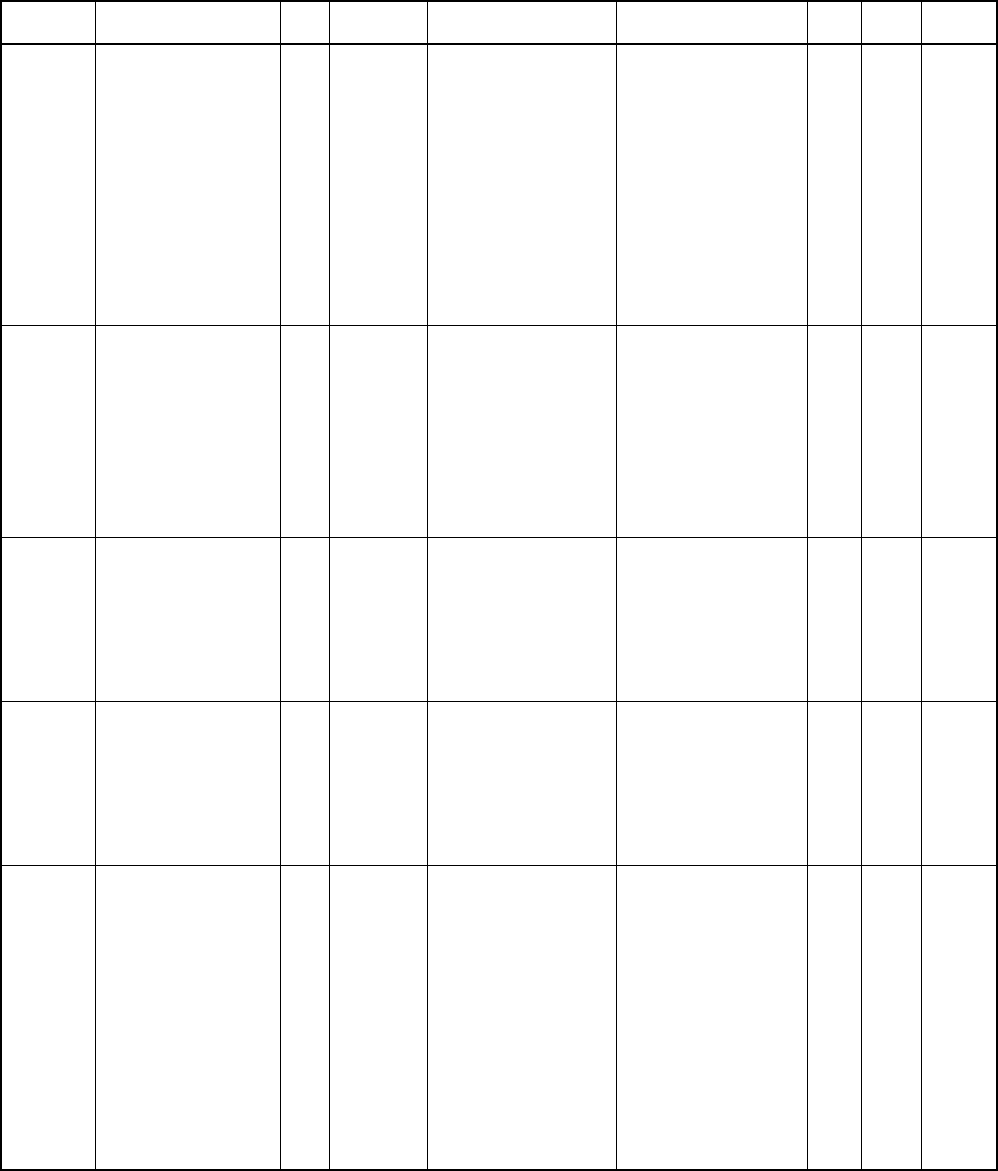

31 CALL ext 6 1 N +2 Address divergence

ahead (L)

10 0

2 −− 00 0

3 SP -1 Return address (L) 0 1 0

4 SP -2 Return address (H) 0 1 0

5 Address divergence

ahead

The following

instruction

10 0

6 Address divergence

ahead +1

The following

following instruction

10 0

21 JMP ext 4 1 N +2 Address divergence

ahead (L)

10 0

2 −− 00 0

3 Address divergence

ahead

The following

instruction

10 0

4 Address divergence

ahead +1

The following

following instruction

10 0

01 MULU A 8 1 N +2 The following

following instruction

10 0

2 −− 00 0

to

8 −− 00 0

11 DIVU A 17 1 N +2 The following

following instruction

10 0

2 −− 00 0

to

17 −− 00 0

− RESET 7 1 −− 00 0

2 0FFFD

H

Mode data 1 0 0

3 0FFFE

H

Reset vector (H) 1 0 0

4 0FFFF

H

Reset vector (L) 1 0 0

5 −− 00 0

6 Start address The following

instruction

10 0

7 Start address +1 The following

following instruction

10 0

Table B-1 Bus Operation List (10/11)

CODE MNEMONIC ~ Cycle Address bus Data bus RD WR RMW