• DR: Data Address Translation. The value of 0 disables translation, and the value of 1 enables

translation.

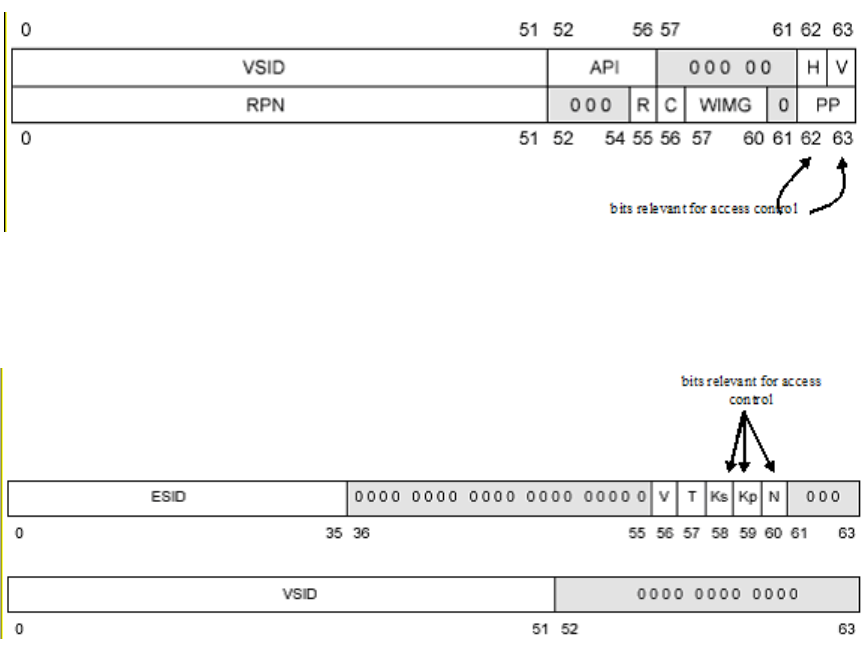

5.5.2.3.2 Page descriptor

Pages are described by Page Table Entries (PTEs). The operating system generates and places PTEs in a page

table in memory. A PTE on SLES is 128 bits in length. Bits relevant to access control are Page protection

bits (PP), which are used with MSR and segment descriptor fields to implement access control.

5.5.2.3.3 Segment descriptor

Segments are described by Segment Table Entries (STEs). The operating system generates and places STEs

in segment tables in memory. Each STE is a 128-bit entry that contains information for controlling segment

search process, and for implementing the memory-protection mechanism.

Ks: Supervisor-state protection key

• Kp: User-state protection key

• N: No-execute protection bit

5.5.2.3.4 Block descriptor

For address translation, a pair of special-purpose registers called upper and lower BAT (Block Address

Translation) registers, which contain effective and physical addresses for the block, define each block.

101

Figure 5-43: Page table entry

Figure 5-44: Segment Table Entry