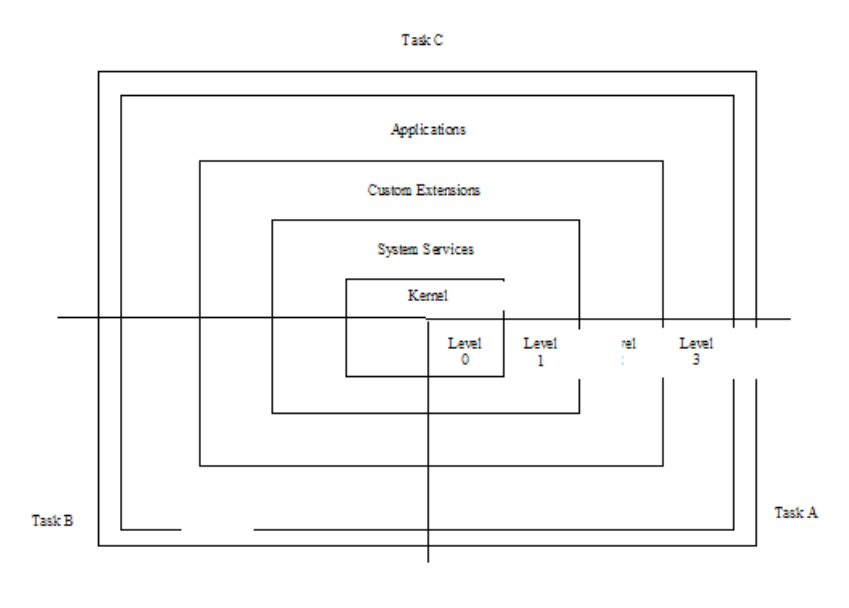

System x: The System x servers are powered by Intel processors. Intel processors provide four execution

modes, identified with processor privilege levels 0 through 3. The highest privilege level execution mode

corresponds to processor privilege level 0; the lowest privilege level execution mode corresponds to processor

privilege level 3. The SLES kernel, as with most other UNIX-variant kernels, utilizes only two of these

execution modes. The highest, with processor privilege level of 0, corresponds to the kernel mode; the

lowest, with processor privilege of 3, corresponds to the user mode.

System p: The System p servers are powered by PowerPC, POWER5 and POWER5+ processors. These

processors provide three execution modes, identified by the PR bit (bit 49) and the HV bit (bit 3) of the

Machine State Register of the processor. Values of 0 for both PR and HV bits indicate a hypervisor execution

mode. An HV bit value of 1, and a PR bit value of 0, indicate a supervisor, or kernel, execution mode. An

HV bit value of 1 and a PR bit value of 1 indicate a user execution mode.

System z: The System z systems also provide two execution modes identified by the Problem State bit (bit

15) of the processor’s Program Status Word (PSW). A value of 0 indicates a supervisor, or kernel, execution

mode, and the value of 1 indicates a problem state, or user, execution mode.

eServer 326: The eServer 326 servers are powered by AMD Opteron processors. These processors provide

four execution modes identified with processor privilege levels 0 through 3. The highest privilege level

execution mode corresponds to processor privilege level 0; the lowest privilege level execution mode

corresponds to processor privilege level 3. The SLES kernel, as with most other UNIX-variant kernels, only

utilizes two of these execution modes. The highest, with processor privilege level of 0, corresponds to the

kernel mode; the lowest, with processor privilege of 3, corresponds to the user mode.

User and kernel modes, which are offered by all of the eServer systems, implement hardware privilege as

follows:

• When the processor is in kernel mode, the program has hardware privilege because it can access and

modify any addressable resources, such as memory, page tables, I/O address space, and memory

management registers. This is not possible in the user mode.

19

Figure 4-1: Levels of Privilege