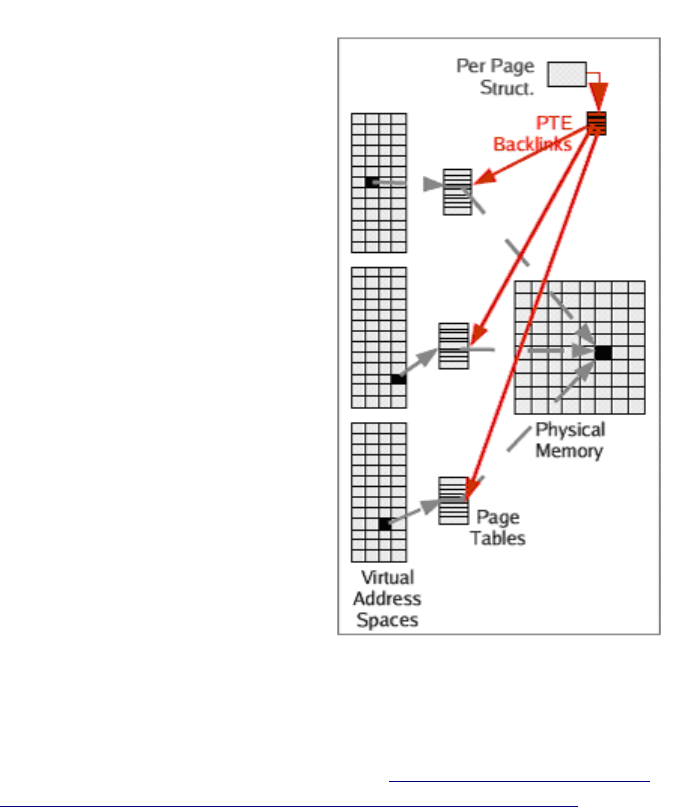

systems, this operation is unacceptably slow. With Rmap VM, additional memory management structures

have been created that enable a physical address to be back-translated to its associated virtual address quickly

and easily.

For more information about Rmap VM, see http://lwn.net/Articles/23732/ and

http://www-106.ibm.com/developerworks/linux/library/l-mem26/.

5.5.3.3 Huge Translation Lookaside Buffers

This memory management feature is valuable for applications that use a large virtual address space. It is

especially useful for database applications. The CPU Translation Lookaside Buffer (TLB) is a small cache

used for storing virtual-to-physical mapping information. By using the TLB, a translation can be performed

without referencing the in-memory page table entry that maps the virtual address. However, to keep

translations as fast as possible, the TLB is typically quite small, so it is not uncommon for large memory

applications to exceed the mapping capacity of the TLB. The HugeTLB feature permits an application to use

a much larger page size than normal, so a single TLB entry can map a correspondingly larger address space.

A HugeTLB entry can vary in size, but, as an example, in an Itanium 2 system a huge page might be 1000

times larger than a normal page. This allows the TLB to map 1000 times the virtual address space of a

normal process without incurring a TLB cache miss. For simplicity, this feature is exposed to applications by

means of a file system interface.

125

Figure 5-65: Rmap VM