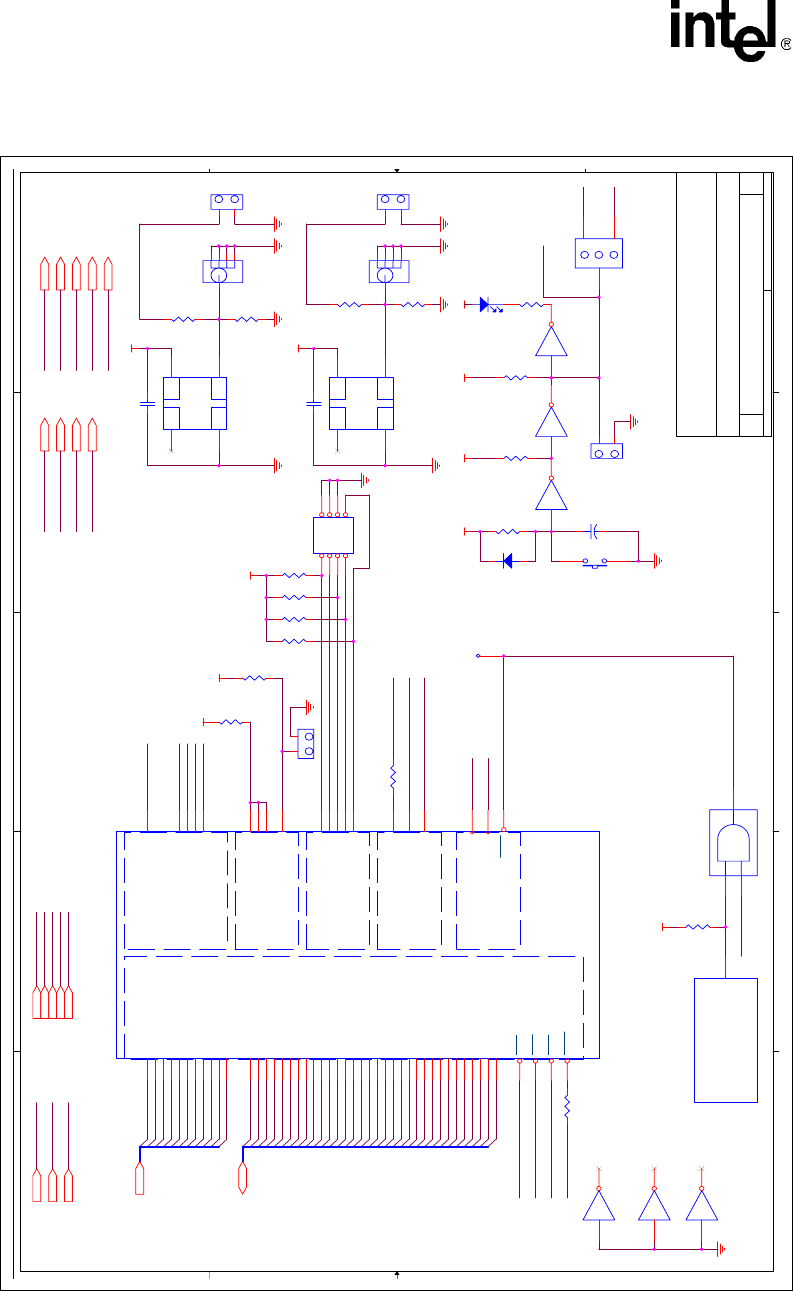

IXD1110 Demo Board

28 Development Kit Manual

Document Number: 250807

Revision Number: 003

Revision Date: June 27, 2003

Figure 7. Intel

®

IXD1110 Control

5

5

4

4

3

3

2

2

1

1

D

D

C

C

B

B

A

A

JTAG PORT

POWER

LED

Note: this board

requires a jumper

on JP2 to work

properly.

X = DO NOT INSTALL

IXF1110 - Control

A1

IXD1110 - FX DEMO Board

Intel Communications Group

9750 Goethe Road

Sacramento, CA 95827

B

214Friday, May 24, 2002

Title

Size Document Number Rev

Date: Sheet

of

uPx_CsN

LED_DATA

LED_CLK

LED_LATCH

uPx_WrN

uPx_RdN

uPx_RdyN

uPx_RdyN

I2C_CLK

IRQ

reset_n

TxPauseFR

TxPauseAdd3

TxPauseAdd2

TxPauseAdd0

TxPauseAdd1

CLK125

LED_DATA

HRESET

POR

reset_n

reset_n

HRESET

POR

I2C_CLK

uPx_Data31

uPx_Data25

uPx_Data10

uPx_Data6

uPx_Data9

uPx_Data2

uPx_Add7

TxPauseAdd0

uPx_Add5

uPx_Data22

uPx_Data19

uPx_Data17

LED_CLK

uPx_Data14

uPx_Data13

uPx_Data12

uPx_Data5

uPx_Add10

uPx_Add3

uPx_Add0

LED_LATCH

uPx_RdN

uPx_Data29

uPx_Data20

uPx_Data8

uPx_Data4

uPx_Data0

CLK50

TxPauseAdd3

uPx_Data16

uPx_Add8

uPx_Add2

CLK50

TxPauseAdd1

uPx_Data27

uPx_Data7

uPx_Data26

uPx_Data3

uPx_Data1

uPx_Add9

uPx_CsN

uPx_Data30

uPx_Data28

uPx_Data24

CLK125

TxPauseAdd2

uPx_WrN

uPx_Data23

uPx_Add4

IRQ

TxPauseFR

uPx_Data18

uPx_Data15

uPx_Add6

uPx_Data21

uPx_Data11

uPx_Add1

uPx_Add[10:0]10,11

uPx_CsN9,11

LED_DATA 8

LED_CLK 8

LED_LATCH 8

uPx_WrN9,11

uPx_RdN9,11

uPx_RdyN 9,11

I2C_CLK 3,4,5,6

TxPauseAdd09,11

TxPauseFR9,11

TxPauseAdd19,11

TxPauseAdd29,11

TxPauseAdd39,11

IRQ 10,11

uPx_Data[31:0]9,10,11

reset_n 8,9

HRESET 10,11

POR 10,11

GND

Vdd_2P5

Vdd_3P3

GND GNDGND

GND

GND

GND

Vdd_3P3

Vdd_3P3

GND

GND

GND

Vdd_2P5

Vdd_3P3Vdd_3P3

GND

GND

GND

Vdd_3P3

Vdd_3P3 Vdd_3P3

DTP6

DIFF TP

+

|

DTP3

DIFF TP

+

|

R1266

4.7k

R4

10K

U5E

SN74HC05

11 10

R7

10K

R14

10K

JP1

HEADER 4X2

12

34

56

78

TP21

1

U3

SM7744DSV-125.0M

1

2

4

3

E/D

GND

VCC

CLK

R2 X

CPU

Pause

Control

GBIC

JTAG

System

LED

Interface

Interface

Interface

Interface

Interface

U1A

IXF1110

J1

G4

F3

H1

E3

E2

G1

C3

F5

F1

C2

B3

A4

B9

A7

C12

E11

C13

A8

A10

A9

E12

A11

G12

E10

F11

D7

D14

C14

F14

A12

A15

G13

B16

E15

G14

A16

C17

A17

B18

A21

B22

C23

F20

A18

H14

C22

J7

G3

G2

J2

K1

B11

B14

G15

L19

AC18

Y24

T16

AA24

N18

A20

A19

K18

AA5

C21

Y4

uP_Add0

uP_Add1

uP_Add2

uP_Add3

uP_Add4

uP_Add5

uP_Add6

uP_Add7

uP_Add8

uP_Add9

uP_Add10

uP_Data0

uP_Data1

uP_Data2

uP_Data3

uP_Data4

uP_Data5

uP_Data6

uP_Data7

uP_Data8

uP_Data9

uP_Data10

uP_Data11

uP_Data12

uP_Data13

uP_Data14

uP_Data15

uP_Data16

uP_Data17

uP_Data18

uP_Data19

uP_Data20

uP_Data21

uP_Data22

uP_Data23

uP_Data24

uP_Data25

uP_Data26

uP_Data27

uP_Data28

uP_Data29

uP_Data30

uP_Data31

uP_Cs

uP_Wr

uP_Rd

uP_Rdy

TxPauseFr

TxPauseAdd0

TxPauseAdd1

TxPauseAdd2

TxPauseAdd3

TX_FAULT_Int

RX_LOS_Int

MOD_DEF_Int

I2C_CLK

TDI

TDO

TMS

TCLK

TRST

LED_DATA

LED_CLK

LED_LATCH

CLK125

CLK50

Sys_Res

R15

220

DTP2

DIFF TP

+

|

S1

RESET

C2 0.01uF

R8 42

R377

10K

IXF1110 Software

Reset

U8K

EP1K30TC144-1-IXF-FX

138

IXF0_reset_n

DTP1

DIFF TP

+

|

U5F

SN74HC05

13 12

R3

4.7k

U5A

SN74HC05

1 2

+

C3

10uF

U4

SM7744HSV-50.0M

1

2

4

3

E/D

GND

VCC

CLK

R13

10K

R5

10K

J22 SMB

1

2

3

4

5

R9 50

U5D

SN74HC05

9 8

JP2

HEADER 3

1

2

3

R16 0

J21 SMB

1

2

3

4

5

D1

LED

1A

1B

1Y

U23A

SN74LV08AD

1

2

3

D2

LL4148

R1141

10K

C1 0.01uF

U5B

SN74HC05

3 4

R1 42

U5C

SN74HC05

5 6

R11 X

R6

10K