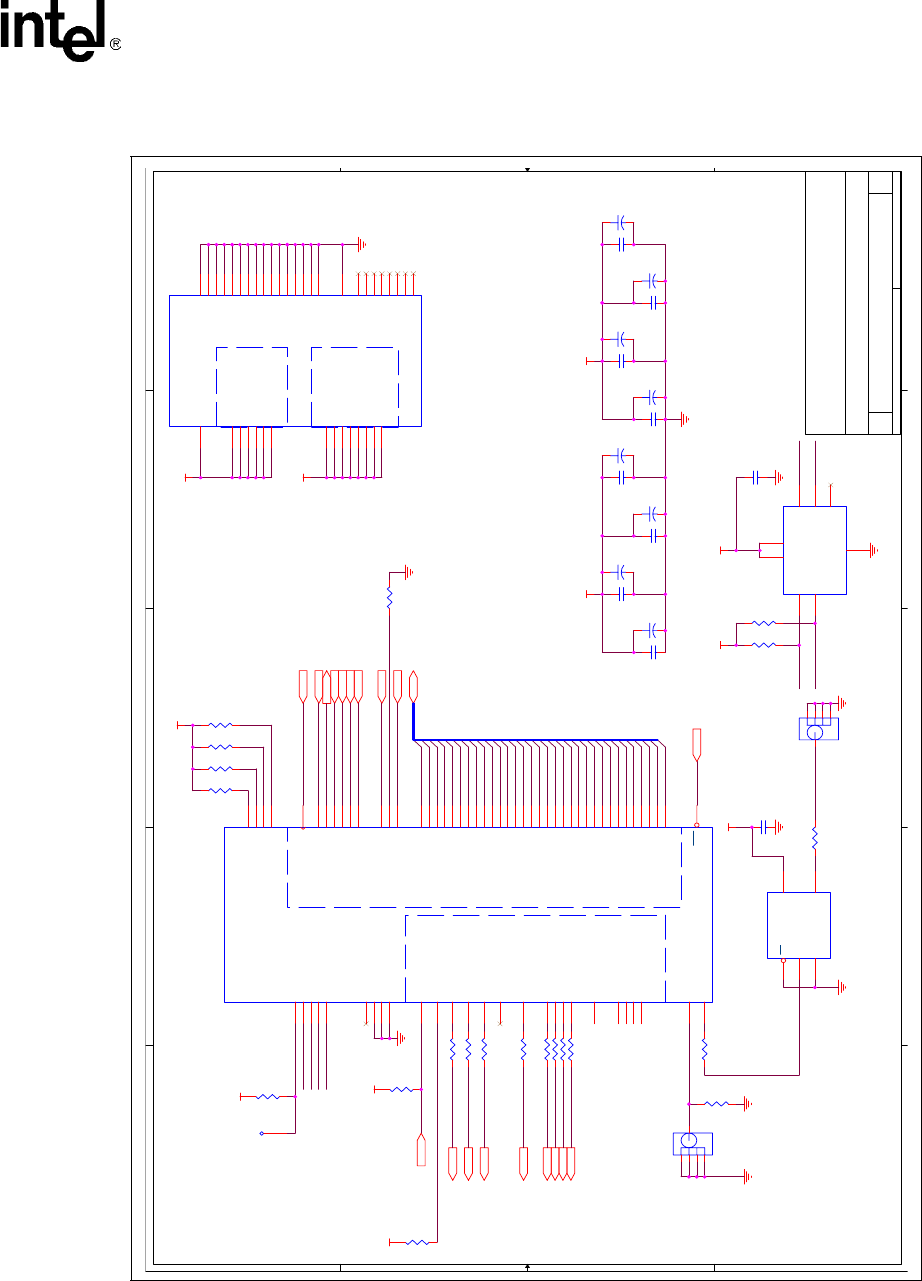

IXD1110 Demo Board

Development Kit Manual 35

Document Number: 250807

Revision Number: 003

Revision Date: June 27, 2003

Figure 14. Intel

®

IXD1110 CPU Interface Control

5

5

4

4

3

3

2

2

1

1

D

D

C

C

B

B

A

A

FPGA Caps

X = DO NOT INSTALL

CPU I/F Control

A1

IXD1110 - FX DEMO Board

Intel Communications Group

9750 Goethe Road

Sacramento, CA 95827

B

914Friday, May 24, 2002

Title

Size Document Number Rev

Date: Sheet

of

Bus_Busy

DCLK

nSTATUS DATA0

CONF_DONE

CONF_DONE

nSTATUS

DATA0

DCLK

nCONFIG

uPx_Data8

uPx_Data26

uPx_Data30

uPx_Data18

uPx_Data28

uPx_Data11

uPx_Data10

uPx_Data1

uPx_Data12

uPx_Data21

uPx_Data27

uPx_Data29

uPx_Data0

uPx_Data3

uPx_Data15

uPx_Data19

uPx_Data25

uPx_Data23

uPx_Data20

uPx_Data4

uPx_Data17

uPx_Data31

uPx_Data2

uPx_Data9

uPx_Data14

uPx_Data24

uPx_Data7

uPx_Data5

uPx_Data6

uPx_Data16

uPx_Data13

uPx_Data22

BUS_CLK

Start_XFER

RD/~WR

Bus_Grant

Bus_Request

GENP_CsN

CsN

reset_n

uPx_RdN

uPx_WrN

uPx_CsN

TxPauseAdd0

TxPauseFR

TxPauseAdd1

TxPauseAdd2

TxPauseAdd3

TA

uPx_RdyN

I2C_CLK_OUT

I2C_CLK_BUF

uPx_Data[31:0] 2,10,11

Bus_Busy 10,11

TxPauseAdd02,11

TxPauseFR2,11

TxPauseAdd12,11

TxPauseAdd22,11

TxPauseAdd32,11

TA 10,11

uPx_WrN2,11

uPx_RdN2,11

uPx_CsN2,11

reset_n 2,8

GENP_CsN 10,11

CsN 10,11

BUS_CLK 10,11

Start_XFER 10,11

Bus_Request 10,11

RD/~WR 10,11

Bus_Grant 10,11

uPx_RdyN2,11

Vdd_3P3

Vdd_3P3Vdd_3P3

GND

GND

Vdd_3P3

Vdd_2P5 Vdd_3P3

GND

GND

GND

Vdd_2P5

Vdd_3P3

GND

GND GND

GND

GND

Vdd_3P3

GND

Vdd_3P3

Vdd_3P3

R224 50

R360

10K

R217

1K

C121

0.022uF

R227 50

R378 50

+3.3V

+2.5V

Power

U8J

EP1K30TC144-1-IXF-FX

53

16

50

75

85

103

127

5

24

45

61

71

94

115

134

6

15

25

40

52

58

66

84

93

104

123

129

139

57

39

56

124

126

42

60

59

128

136

137

141

VCC_CKLK

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND_CKLK

NC

GND

GND

GND

NC

NC

NC

NC

NC

NC

NC

R220

10K

R223 50

TP1

1

+

C108

0.22uF

R1265

1K

R218

1K

C118

0.022uF

+

C117

0.22uF

+

C115

0.22uF

IXF1110 Interface

CPU Bus Interface

IXF1110 & CPU Interfaces

U8A

EP1K30TC144-1-IXF-FX

55

69

72

65

70

68

67

79

78

73

80

81

82

83

86

87

88

89

90

91

92

95

96

97

98

99

100

101

102

109

110

111

112

113

114

116

117

118

119

120

121

122

17

20

21

18

19

135

133

132

131

130

41

43

44

46

47

54

105

34

1

4

74

2

35

107

108

3

77

76

106

22

125

140

bus_clk

TS_n

TA_n

RD_WR_n

Bus_busy_n

Bus_grant_n

Bus_request_n

IXF_CsN

IXF_Sel

GenP_CsN

cpu_DATA0

cpu_DATA1

cpu_DATA2

cpu_DATA3

cpu_DATA4

cpu_DATA5

cpu_DATA6

cpu_DATA7

cpu_DATA8

cpu_DATA9

cpu_DATA10

cpu_DATA11

cpu_DATA12

cpu_DATA13

cpu_DATA14

cpu_DATA15

cpu_DATA16

cpu_DATA17

cpu_DATA18

cpu_DATA19

cpu_DATA20

cpu_DATA21

cpu_DATA22

cpu_DATA23

cpu_DATA24

cpu_DATA25

cpu_DATA26

cpu_DATA27

cpu_DATA28

cpu_DATA29

cpu_DATA30

cpu_DATA31

uPx_RdyN_0

uPx_RdN

uPx_WrN

uPx_CsN_0

uPx_CsN_1

IXF0_TxPauseFR

IXF0_TxPauseAdd0

IXF0_TxPauseAdd1

IXF0_TxPauseAdd2

IXF0_TxPauseAdd3

IXF1_TxPauseFR

IXF1_TxPauseAdd0

IXF1_TxPauseAdd1

IXF1_TxPauseAdd2

IXF1_TxPauseAdd3

reset

TDI

TMS

TCK

TDO

nCONFIG

CONF_DONE

nSTATUS

DCLK

DATA0

nCEO

MSEL0

MSEL1

nCE

uPx_RdyN_1

clk_in

I2C_CLK_IXF0_OUT

R228 50

C119

0.022uF

+

C107

0.22uF

R219

1K

C111

0.022uF

+

C106

0.22uF

R1264

1K

U18

EPC1PC8

2

3

4

6

1

8

7

5

DCLK

OE

nCS

nCASC

DATA

VCC

VCC

GND

R226 50

U22

NC7SZ125M5

1

2

3 4

5

OE

A

GND Y

VCC

R358 50

R229 50

J26 SMB

1

2

3

4

5

C113

0.022uF

C112

0.022uF

R222 50

R216

1K

J25 SMB

1

2

3

4

5

C122

0.01uF

+

C114

0.22uF

R236

10K

R230 50

R237

10K

C291

0.01uF

+

C109

0.22uF

C120

0.022uF

R116 0

C110

0.022uF

+

C116

0.22uF