Timers

16-Bit Timer Setup Examples

MN102H75K/F75K/85K/F85K LSI User Manual Panasonic Semiconductor Development Company

99

Panasonic

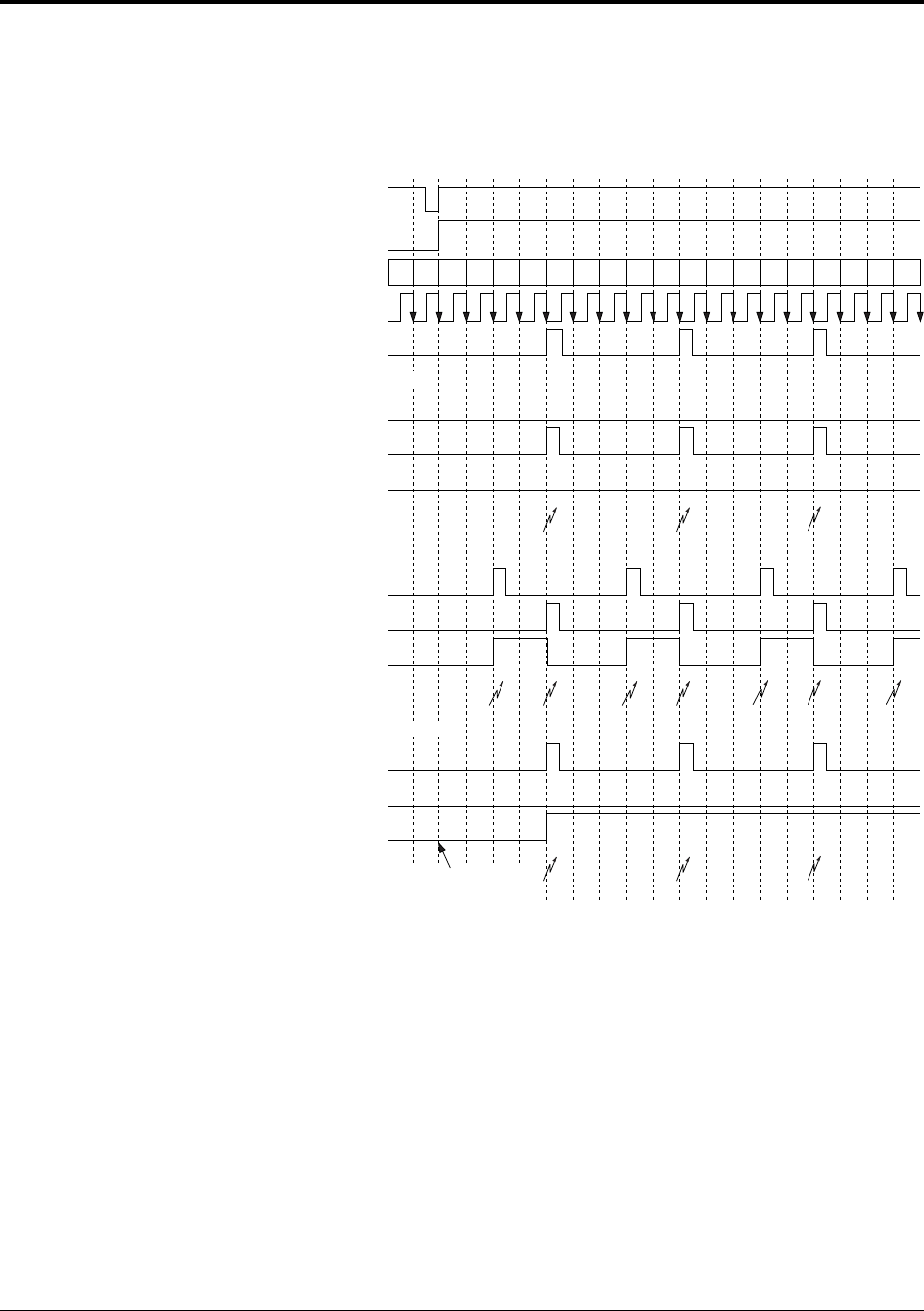

Figure 4-30 below shows the output waveforms for TM4OA. Both A and B

interrupts can occur, but B interrupts can only occur if the TM4CB setting is from

0 to less than TM4CA. This is because when TM4CB ≤ TM4CA, TM4BC never

matches TM4CB.

Figure 4-30 Single-Phase PWM Output Timing (Timer 4)

Write to TM4MD

TM4EN

TM4BC

B

OSC

/4

CLRBC4

S4

R4

TM4OA

Interrupts

012340 01234012340123

AB

AB

AB

B

A

B

A

B B

A

(1) TMCB = 4 (All 0s)

S4

R4

TM4OA

Interrupts

(2) TMCB = 2

A

A

A

S4

R4

TM4OA

Interrupts

0s on first cycle, since

S4 has not gone high yet.

(3) TMCB = FFFF (All 1s)