Closed-Caption Decoder

Functional Description

MN102H75K/F75K/85K/F85K LSI User Manual Panasonic Semiconductor Development Company

231

Panasonic

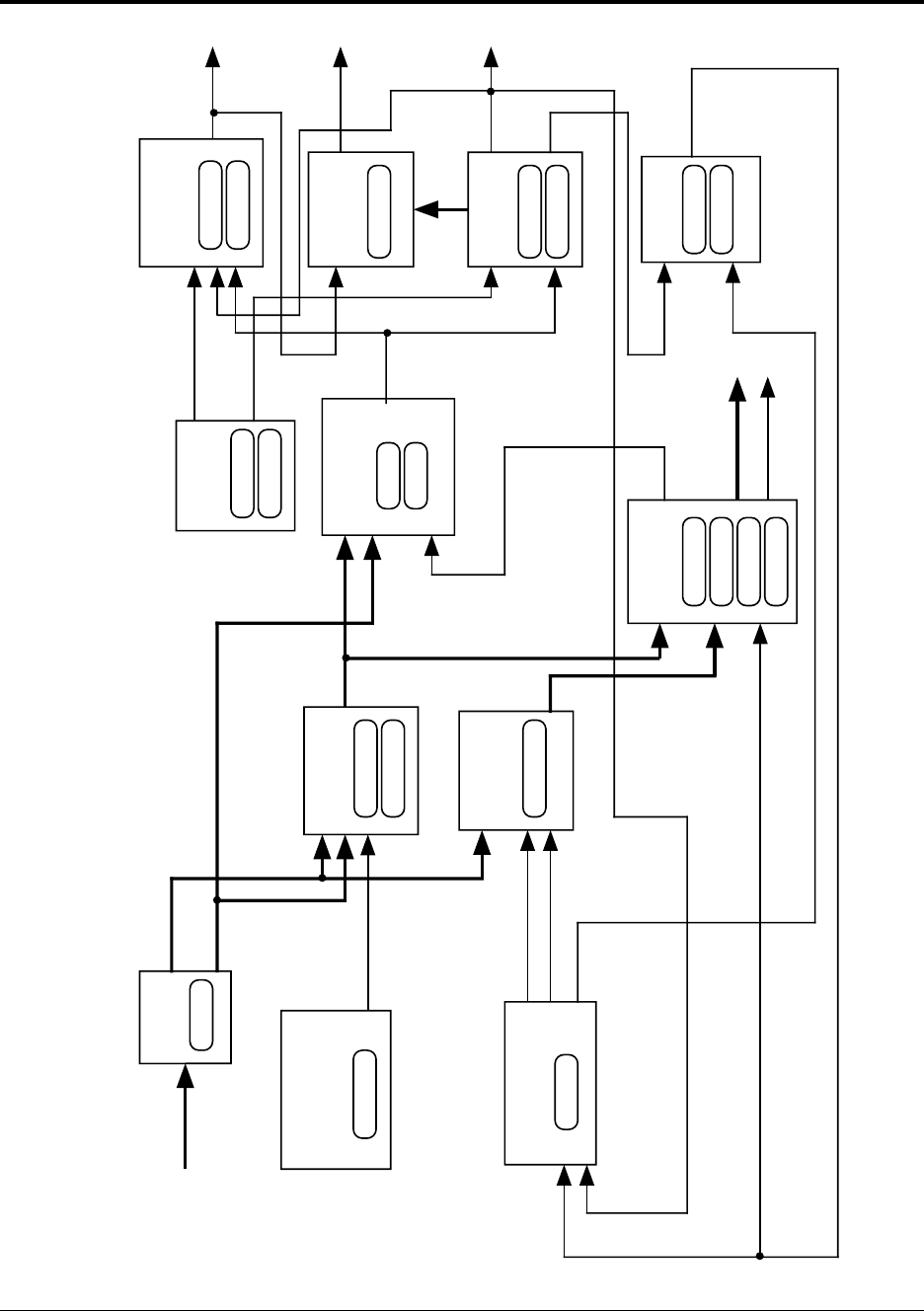

Figure 9-6 Sync Separator Circuit Block Diagram

LPF

MING

CLMODE[1:0]

CLM

Clamp control

pulse signal

ADDATA[7:0]

NFSW[1:0]

LPF1OUT[6:0]

LPFOUT[6:0]

SCMING[9:0]

MINP

Minimum sync tip

load pulse generator

Minimum sync tip

detector

SYNCMIN[6:0]

Pedestal level

detector

BPLV[6:0]

BPLV[6:0]

BPPG

BPGATE

HP

Backporch gate level

generator

BPPST[8:0]

Clamping

controller

SAFE

VBION

PCLV[6:0]

CVBSSEL

HLOCKLV[8:0]

BCSEL

HLOCK

Sync separator

pulse generator

VSEPSAMP

HSEPSAMP

VSYNC separator

HSYNC separator

Field detector

Sync detector

Composite

sync separator

FQDIV[3:0]

VFQDIV[5:0]

PSP[5:0]

BSP[5:0]

COMPSY

VSEP

ODDEVEN

HSEP

HSEPCORP

VSEPLMT[2:0]

VSEPSEL

VPHASE[9:0]

HCLOSEE[9:0]

HSFREQ[10:0]

CNT11B[10:0]

SYNCMIN[6:0]