Timers

8-Bit Timer Setup Examples

MN102H75K/F75K/85K/F85K LSI User Manual Panasonic Semiconductor Development Company

83

Panasonic

TM0UDICL (example) x’00FC74’

TM0UDICH (example) x’00FC75’

4. Set the divide-by ratio for timer 0. Since the timer will count 4 TM0IO

cycles, write x’03’ to the timer 0 base register (TM0BR). (The valid range

for TM0BR is 0 to 255.)

TM0BR (example) x’00FE10’

Do not change the clock source

once you select it. Selecting the

clock source while you set up

the count operation control will

corrupt the value in the binary

counter.

5. Set the TM0LD bit of the TM0MD register to 1. This loads the value in the

base register to the binary counter. At the same time, select the clock source

as the TM0IO signal input by writing b’11’ to TM0S[1:0].

TM0MD (example) x’00FE20’

In the bank and linear address-

ing versions of the MN102

series, it was necessary to set

TM0EN and TM0LD to 0

between steps 5 and 6, to

ensure stable operation. This is

unnecessary in the high-speed

linear addressing version.

6. Set TM0LD to 0 and TM0EN to 1. This starts the timer. Counting begins at

the start of the next cycle. When the binary counter reaches 0 and loads the

value x’03’ from the base register, in preparation for the next count, a timer 0

underflow interrupt request is sent to the CPU.

Bit:76543210

———

TM0UD

IR

———

TM0UD

ID

Setting:00000000

Bit:76543210

———————

TM0UD

IE

Setting:00000001

Bit:76543210

TM0

BR7

TM0

BR6

TM0

BR5

TM0

BR4

TM0

BR3

TM0

BR2

TM0

BR1

TM0

BR0

Setting:00000011

Bit:76543210

TM0

EN

TM0

LD

————

TM0

S1

TM0

S0

Setting:01000011

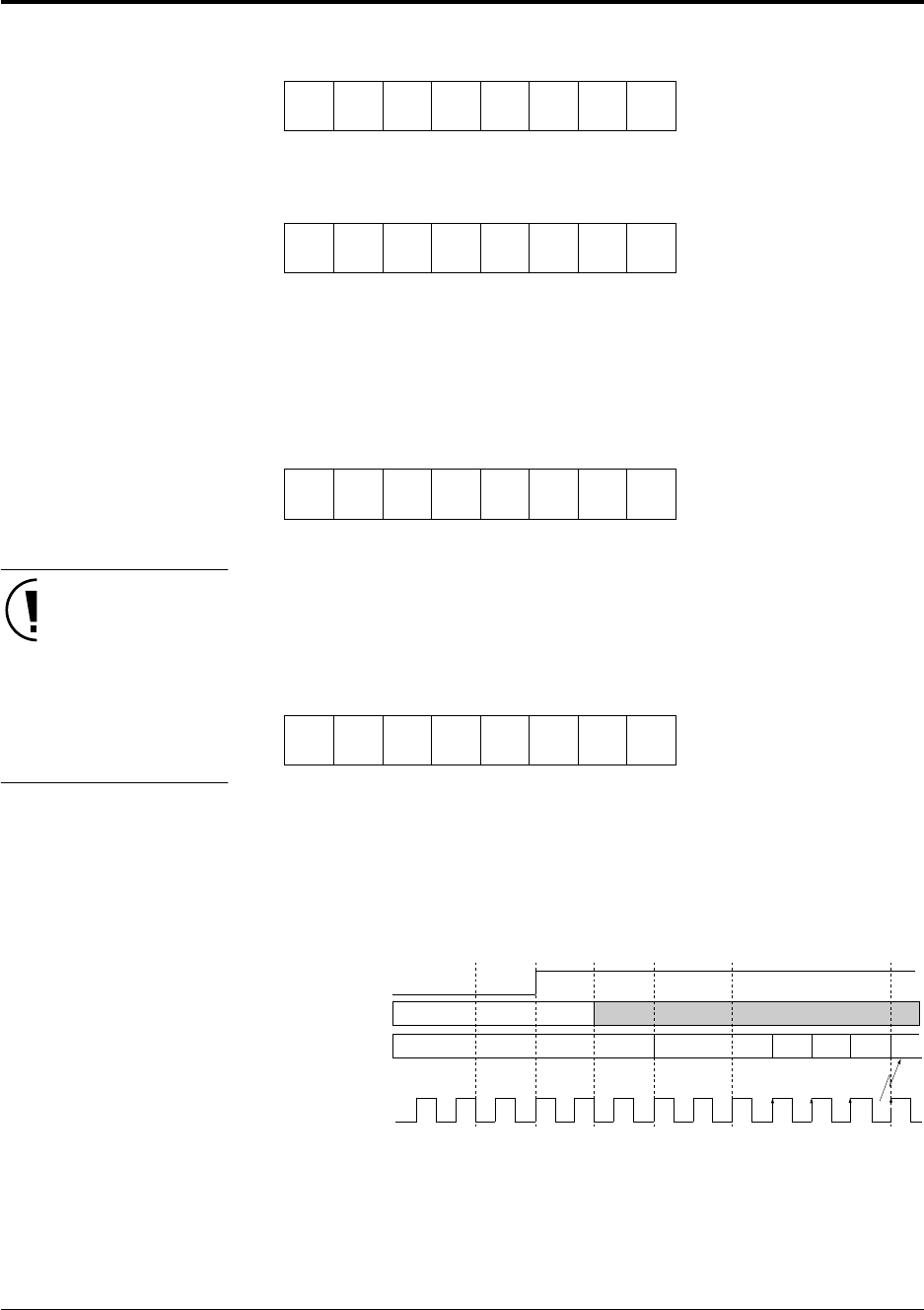

Figure 4-10 Event Counter Timing (Timer 0)

Interrupt enable

TM0BR

TM0BC

Timer 0 underflow

interrupt

TM0IO

(2)

(4)

(5)

(3) (6)

TM0BR(B)

TM0MD(B)

TM0UDICH(B) TM0MD(B)

00 03

00 03 02 01 00 03

Sequence