Matrox Meteor-II MJPEG Module 73

JPEG Processor During compression, the JPEG Processor receives the 8 x 8

pixel blocks and compresses them according the JPEG

standard. Both lossy and lossless formats are supported.

During decompression, the JPEG Processor decompresses the

data, and transfers the 8 x 8 pixel blocks to the Color Space

Converter.

MJPEG FPGA The MJPEG FPGA controls the direction of compressed and

decompressed data and generates control signals on the

module. It implements a bus handshake with the VIA on the

baseboard to access the SGRAM. The SGRAM on the baseboard

is used to store the compressed data.

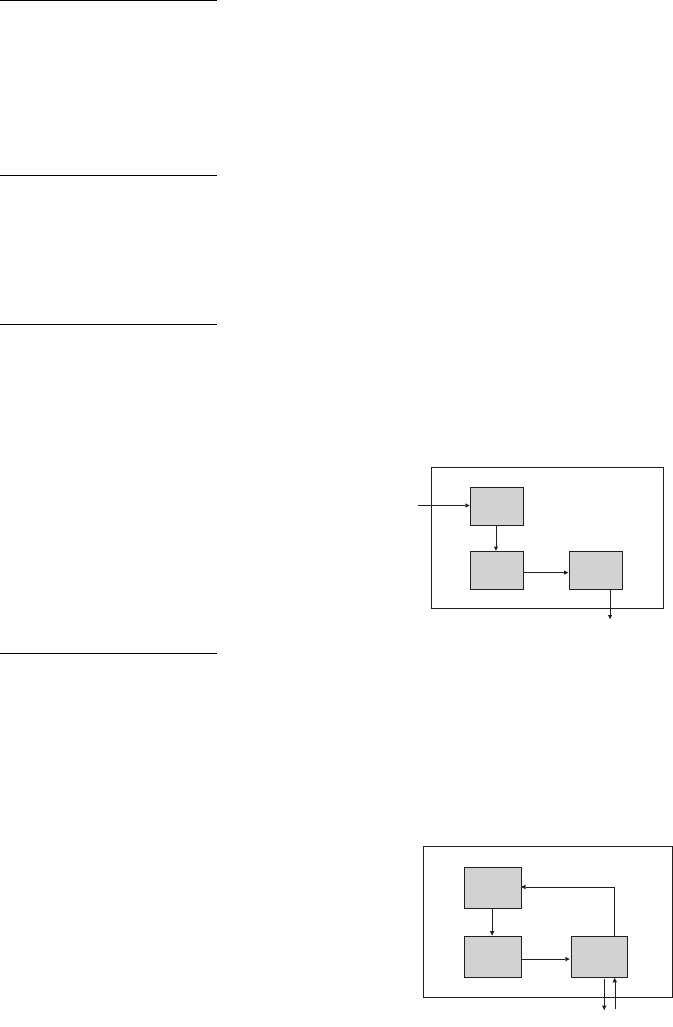

Encoding MJPEG During MJPEG (interlaced) compression, the baseboard grabs

a field of data. This data enters the module through the

Meteor-II grab port, and passes through the Color Space

Converter, the JPEG Processor, and finally exits the module to

the Host through the memory port on the MJPEG FPGA chip.

Encoding JPEG During JPEG (non-interlaced) compression, the baseboard

grabs an entire frame of data. This data enters the module

through the memory port on the MJPEG FPGA chip and passes

through the Color Space Converter. From there, JPEG

compression follows the same path as MJPEG compression.

Compressing an archived video stream is supported under

JPEG compression.

Host

Host