119

8170 N/B MAINTENANCE

5.2 Intel 82845(Brookdale Memory Controller HUB)

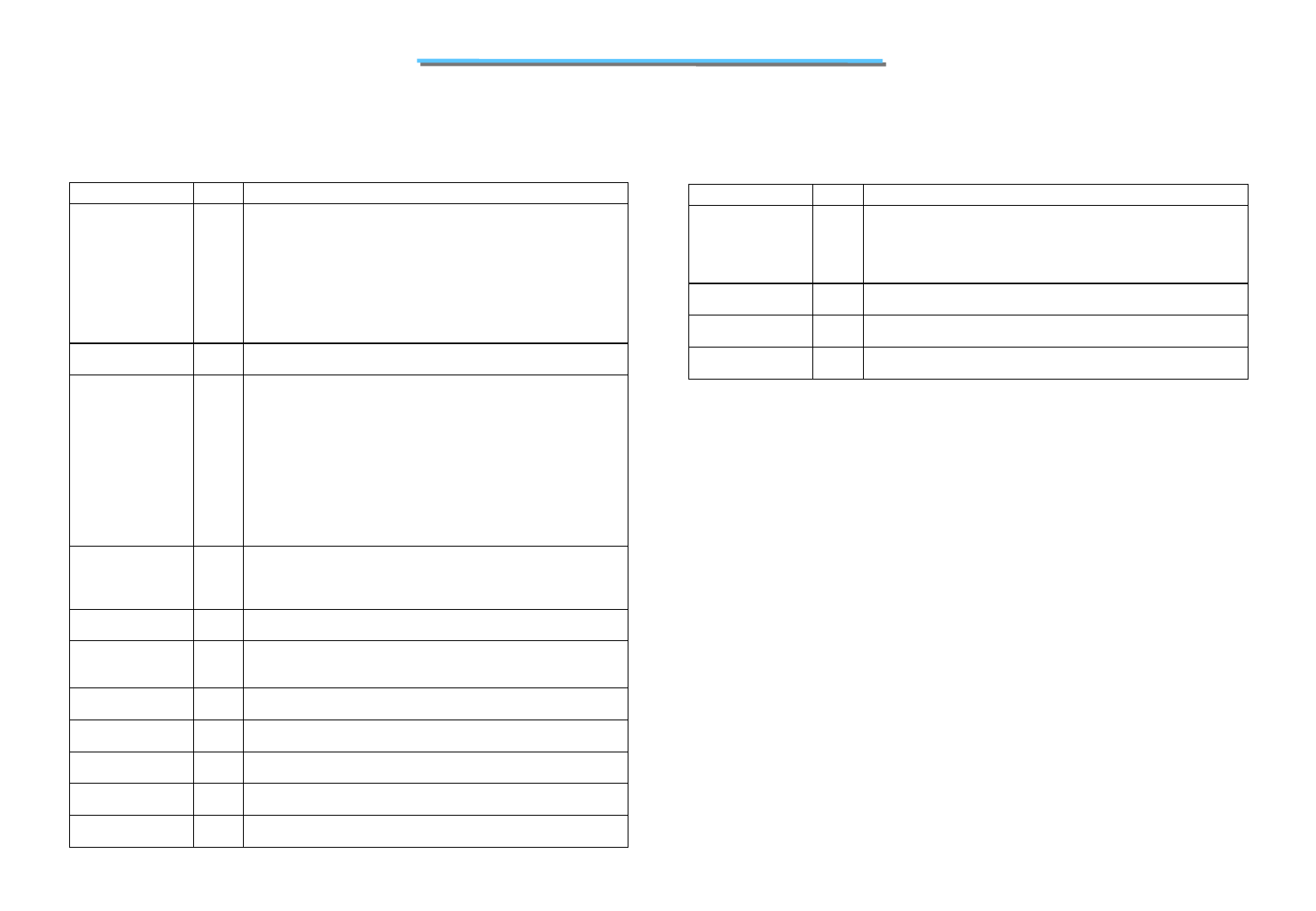

System Bus singnals

Name Type Description

HREQ[4:0]#

I/O

AGTL+

Host Request Command: These signals define the attributes of the

request. In Enhanced Mode HREQ[4:0]# are transferred at 2x rate.

HREQ[4:0]# are asserted by the requesting agent during both halves

of Request Phase. In the first half the signals define the transaction

type to level of detail that is sufficient to begin a snoop request. In the

second half the signals carry additional information to define the

complete transaction type.

The transactions supported by the MCH host bridge are defined in the

Section 5.1.

HTRDY#

I/O

AGTL+

Host Target Ready: HTRDY# indicates that the target of the

processor transaction is able to enter the data transfer phase.

RS[2:0]#

O

AGTL+

Response Status: RS[2:0]# indicates the type of response according

to the following the table:

RS[2:0] Response Type

000 Idle state

001 Retry response

010 Deferred response

011 Reserved (not driven by MCH)

100 Hard Failure (not driven by MCH)

101 No data response

110 Implicit Write back

111 Normal data response

SCS[11:0]#

O

AGTL+

Chip Select: These signals select the particular SDRAM components

during the active state.

Note: There are two SCS# signals per SDRAM row. These signals

can be toggled on every rising system memory clock edge.

SMA[12:0]

O

AGTL+

Multiplexed Memory Address: These signals are used to provide

the multiplexed row and column address to SDRAM.

SBS[1:0]

O

AGTL+

Memory Bank Select: SBS[1:0] define the banks that are selected

within each SDRAM row. The SMA and SBS signals combine to

address every possible location in a SDRAM device.

SRAS#

O

AGTL+

SDRAM Row Address Strobe: SRAS# is Used with SCAS# and

SWE# (along with SCS#) to define the DRAM commands.

SCAS#

O

AGTL+

SDRAM Column Address Strobe: SCAS# is used with SRAS#

andSWE# (along with SCS#) to define the SDRAM commands.

SWE#

O

AGTL+

Write Enable: SWE# is used with SCAS# and SRAS# (along with

SCS#) to define the SDRAM commands.

SDQ[63:0]

I/O

AGTL+

Data Lines: These signals are used to interface to the SDRAM data

bus.

SCB[7:0]

I/O

AGTL+

Check Bit Data Lines: These signals are used to interface to the

SDRAM ECC signals.

Name Type Description

SCKE[5:0]

O

AGTL+

Clock Enable: These pins are used to signal a self-refresh or

Powerdown command to a SDRAM array when entering system

suspend. SCKE is also used to dynamically powerdown inactive

SDRAM rows. There is one SCKE per SDRAM row. These signals

can be toggled on every rising SCLK edge.

RDCLKO

O

AGTL+

Clock Output: RDCLKO is used to emulate source-synch clocking

for reads. This signal connects to RDCLKIN.

SMA[12:0]

O

AGTL+

Multiplexed Memory Address: These signals are used to provide

the multiplexed row and column address to SDRAM.

RDCLKIN

I

AGTL+

Clock Input: RDCLKIN is used to emulate source-synch clocking

for reads. This signal connects to RDCLKO.