124

8170 N/B MAINTENANCE

5.3 Intel 82801BA(I/O Controller HUB )

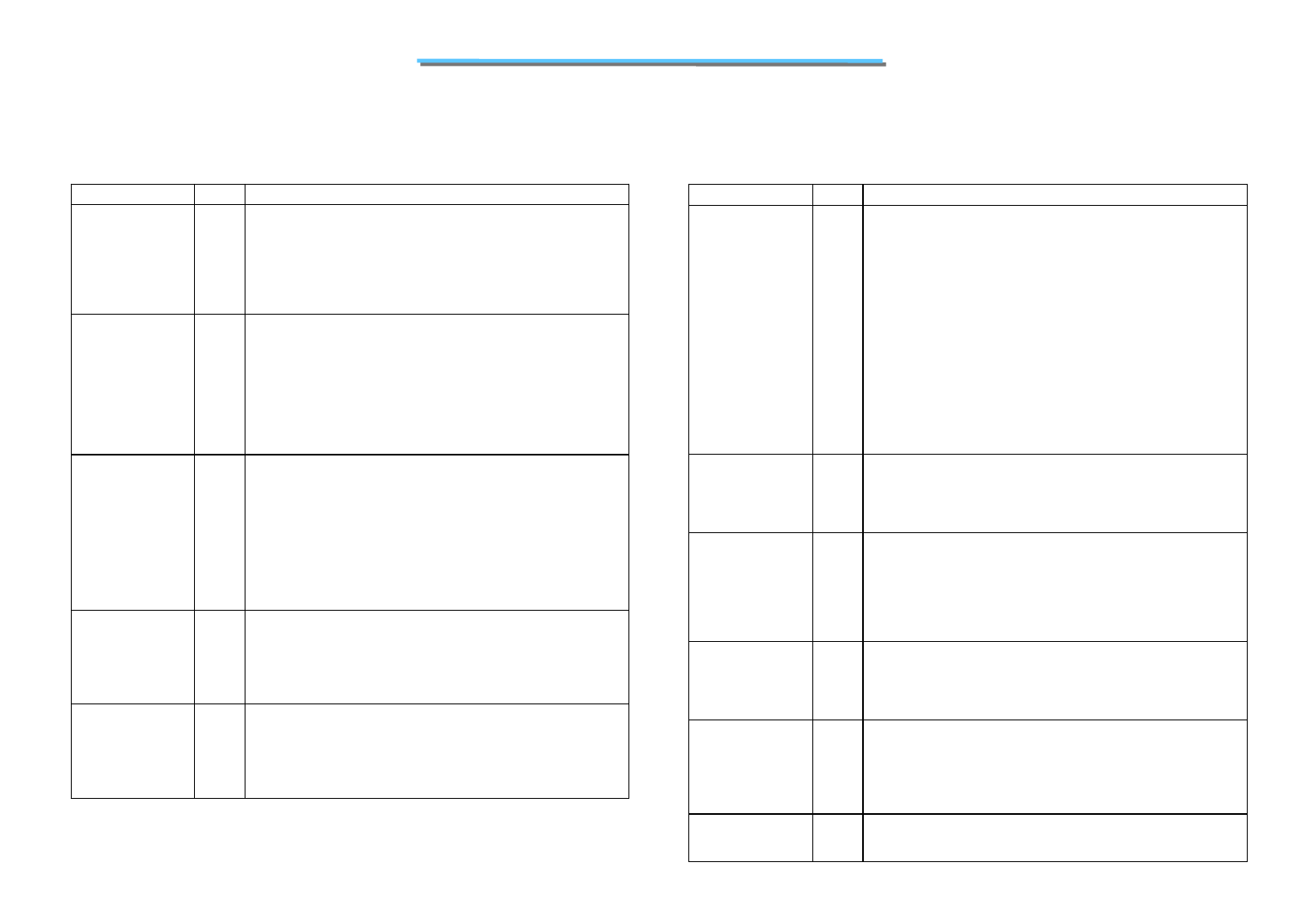

PCI Interface Signals

Name Type Description

FRAME#

I/O Cycle Frame: The current Initiator drives FRAME# to indicate the

beginning and duration of a PCI transaction. While the initiator

asserts FRAME#, data transfers continue. When the initiator negates

FRAME#, the transaction is in the final data phase. FRAME# is an

input to the ICH2 when the ICH2 is the target, and FRAME# is an

output from the ICH2 when the ICH2 is the Initiator. FRAME#

remains tri-stated by the ICH2 until driven by an Initiator.

IRDY#

I/O

Initiator Ready: IRDY# indicates the ICH2's ability, as an Initiator,

to complete the current data phase of the transaction. It is used in

conjunction with TRDY#. A data phase is completed on any clock

both IRDY# and TRDY# are sampled asserted. During a write,

IRDY# indicates the ICH2 has valid data present on AD[31:0].

During a read, it indicates the ICH2 is prepared to latch data. IRDY#

is an input to the ICH2 when the ICH2 is the Target and an output

from the ICH2 when the ICH2 is an Initiator. IRDY# remains

tri-stated by the ICH2 until driven by an Initiator.

TRDY#

I/O

Target Ready: TRDY# indicates the ICH2's ability as a Target to

complete the current data phase of the transaction. TRDY# is used in

conjunction with IRDY#. A data phase is completed when both

TRDY# and IRDY# are sampled asserted. During a read, TRDY#

indicates that the ICH2, as a Target, has placed valid data on

AD[31:0]. During a write, TRDY# indicates the ICH2, as a Target is

prepared to latch data. TRDY# is an input to the ICH2 when the ICH2

is the Initiator and an output from the ICH2 when the ICH2 is a

Target. TRDY# is tri-stated from the leading edge of PCIRST#.

TRDY# remains tri-stated by the ICH2 until driven by a target.

STOP#

I/O

Stop: STOP# indicates that the ICH2, as a Target, is requesting the

Initiator to stop the current transaction. STOP# causes the ICH2, as an

Initiatior, to stop the current transaction. STOP# is an output when the

ICH2 is a target and an input when the ICH2 is an Initiator. STOP# is

tri-stated from the leading edge of PCIRST#. STOP# remains

tri-stated until driven by the ICH2.

REQ[0:4]#

REQ[5]# /

REQ[B]# /

GPIO[1]

I PCI Requests: The ICH2 supports up to 6 masters on the PCI bus.

REQ[5]# is muxed with PC/PCI REQ[B]# (must choose one or the

other, but not both). If not used for PCI or PC/PCI,

REQ[5]#/REQ[B]# can instead be used as GPIO[1].

Note: REQ[0]# is programmable to have improved arbitration latency

for supporting PCI-based 1394 controllers.

Name Type Description

PAR

I/O

Calculated/Checked Parity: PAR uses "even" parity calculated on

36 bits, AD[31:0] plus C/BE[3:0]#. "Even" parity means that the

ICH2 counts the number of 1s within the 36 bits plus PAR and the

sum is always even. The ICH2 always calculates PAR on 36 bits,

regardless of the valid byte enables. The ICH2 generates PAR for

address and data phases and only guarantees PAR to be valid one PCI

clock after the corresponding address or data phase. The ICH2 drives

and tri-states PAR identically to the AD[31:0] lines except that the

ICH2 delays PAR by exactly one PCI clock. PAR is an output during

the address phase (delayed one clock) for all ICH2 initiated

transactions. PAR is an output during the data phase (delayed one

clock) when the ICH2 is the Initiator of a PCI write transaction, and

when it is the target of a read transaction. ICH2 checks parity when it

is the target of a PCI write transaction. If a parity error is detected, the

ICH2 sets the appropriate internal status bits, and has the option to

generate an NMI# or SMI#.

PERR#

I/O

Parity Error: An external PCI device drives PERR# when it receives

data that has a

p

arity error. The ICH2 drives PERR# when it detects a

parity error. The ICH can either generate an NMI# or SMI# upon

detecting a parity error (either detected internally or reported via the

PERR# signal).

GNT[0:4]#

GNT[5]# /

GNT[B]# /

GPIO[17]#

O

PCI Grants: The ICH2 supports up to 6 masters on the PCI bus.

GNT[5]# is muxed with PC/PCI GNT[B]# (must choose one or the

other, but not both). If not needed PCI or PC/PCI, GNT[5]# can

instead be used as a GPIO.

Pull-up resistors are not required on these signals. If pullups are used,

they should be tied to the Vcc3_3 power rail.

GNT[B]#/GNT[5]#/GPIO[17] has an internal pullup.

PCICLK

I

PCI Clock: This is a 33 MHz clock. PCICLK provides timing for all

transactions on the PCI Bus. .

Note:For 82801BAM ICH2-M, this clock does not stop based on the

STP_PCI# signal. The PCI Clock only stops based on SLP_S1# or

SLP_S3#.

PCIRST#

O

PCI Reset: ICH2 asserts PCIRST# to reset devices that reside on the

PCI bus. The ICH2 asserts PCIRST# during power-up and when S/W

initiates a hard reset sequence through the RC (CF9h) register. The

ICH2 drives PCIRST# inactive a minimum of 1 ms after PWROK is

driven active. The ICH2 drives PCIRST# active a minimum of 1 ms

when initiated through the RC register.

SERR#

I System Error: SERR# can be pulsed active by any PCI device that

detects a system error condition. Upon sampling SERR# active, the

ICH2 has the ability to generate an NMI, SMI#, or interrupt.