125

8170 N/B MAINTENANCE

5.3 Intel 82801BA(I/O Controller HUB )

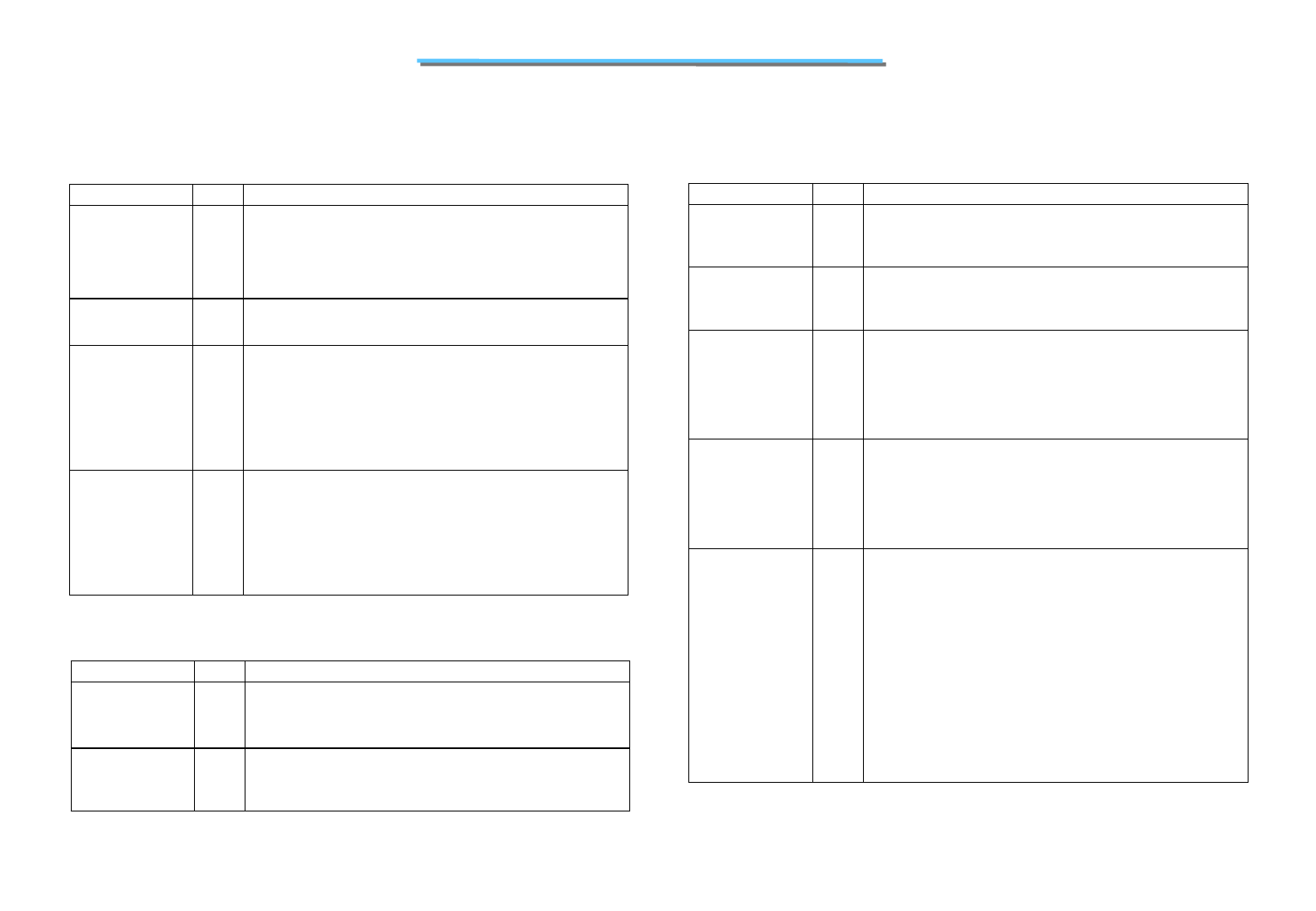

PCI Interface Signals

Name Type Description

PME#

I

PCI Power Management Event: PCI peripherals drive PME# to

wake the system from low-power states S1–S5. PME# assertion can

also be enabled to generate SCI from the S0 state. In some cases the

ICH2 may drive PME# active due to an internal wake event. The

ICH2 will not drive PME# high, but it will be pulled up to VccSus3_3

by an internal pull-up resistor.

CLKRUN#

(ICH2-M only)

I/O

PCI Clock Run: For the ICH2-M, CLKRUN# is used to support PCI

Clock Run protocol. This signal connects to PCI devices that need to

request clock re-start or prevention of clock stopping.

REQ[A]# /

GPIO[0]

REQ[B]# /

REQ[5]# /

GPIO[1]

I

PC/PCI DMA Request [A:B]: This request serializes ISA-like DMA

Requests for the purpose of running ISA-compatible DMA cycles

over the PCI bus. This is used by devices such as PCI-based Super

I/O or audio codecs that need to perform legacy 8237 DMA but have

no ISA bus.

When not used for PC/PCI requests, these signals can be used as

General Purpose Inputs. Instead, REQ[B]# can be used as the 6th PCI

bus request.

GNT[A]# /

GPIO[16]

GNT[B]# /

GNT[5]# /

GPIO[17]

O

PC/PCI DMA Acknowledges [A:B]: This grant serializes an

ISA-like DACK# for the purpose of running DMA/ISA master cycles

over the PCI bus. This is used by devices such as PCI-

b

ased Super/IO

or audio codecs which need to perform legacy 8237 DMA but have

no ISA bus.

When not used for PC/PCI, these signals can be used as General

Purpose Outputs. GNTB# can also be used as the 6th PCI bus master

grant output. These signal have internal pull-up resistors.

IDE Interface Signals

Name Type Description

PDCS1#,

SDCS1#

O

Primary and Secondary IDE Device Chip Selects for 100 Range:

These signals are for the ATA command register block. This output

signal is connected to the corresponding signal on the primary or

secondary IDE connector.

PDCS3#,

SDCS3#

O

Primary and Secondary IDE Device Chip Select for 300 Range:

These signals are for the ATA control register block. This output

signal is connected to the corresponding signal on the primary or

secondary IDE connector.

IDE Interface Signals(continued)

Name Type Description

PDA[2:0],

SDA[2:0]

O

Primary and Secondary IDE Device Address: These output signals

are connected to the corresponding signals on the primary or

secondary IDE connectors. They are used to indicate which byte in

either the ATA command block or control block is being addressed.

PDD[15:0],

SDD[15:0]

I/O

Primary and Secondary IDE Device Data: These signals directly

drive the corresponding signals on the primary or secondary IDE

connector. There is a weak internal pull-down resistor on PDD[7] and

SDD[7].

PDDREQ,

SDDREQ

I

Primary and Secondary IDE Device DMA Request: These input

signals are directly driven from the DRQ signals on the primary or

secondary IDE connector. It is asserted by the IDE device to request a

data transfer, and used in conjunction with the PCI bus master IDE

function. They are not associated with

any AT-compatible DMA channel. There is a weak internal

pull-down resistor on these signals.

PDDACK#,

SDDACK#

O Primary and Secondary IDE Device DMA Acknowledge: These

signals directly drive the DAK# signals on the primary and secondary

IDE connectors. Each signal is asserted by the ICH2 to indicate to the

IDE DMA slave devices that a given data transfer cycle (assertion of

DIOR# or DIOW#) is a DMA data transfer cycle. This signal is used

in conjunction with the PCI bus master IDE function and are not

associated with any AT-compatible DMA channel.

PDIOR#

SDIOR#

O

Primary and Secondary Disk I/O Read (PIO and Non-Ultra

DMA): This is the command to the IDE device that it may drive data

on the PDD or SDD lines. Data is latched by the ICH2 on the

deassertion edge of PDIOR# or SDIOR#. The IDE device is selected

either by the ATA register file chip selects (PDCS1# or SDCS1#,

PDCS3# or SDCS3#) and the PDA or SDA lines, or the IDE DMA

acknowledge (PDDAK# or SDDAK#).

Primary and Secondary Disk Write Strobe (Ultra DMA Writes to

Disk): This is the data write strobe for writes to disk. When writing to

disk, ICH2 drives valid data on rising and falling edges of PDWSTB

or SDWSTB.

Primary and Secondary Disk DMA Ready (Ultra DMA Reads

from Disk): This is the DMA ready for reads from disk. When

reading from disk, ICH2 deasserts PRDMARDY# orSRDMARDY#

to pause burst data transfers.