122

8170 N/B MAINTENANCE

5.2 Intel 82845(Brookdale Memory Controller HUB)

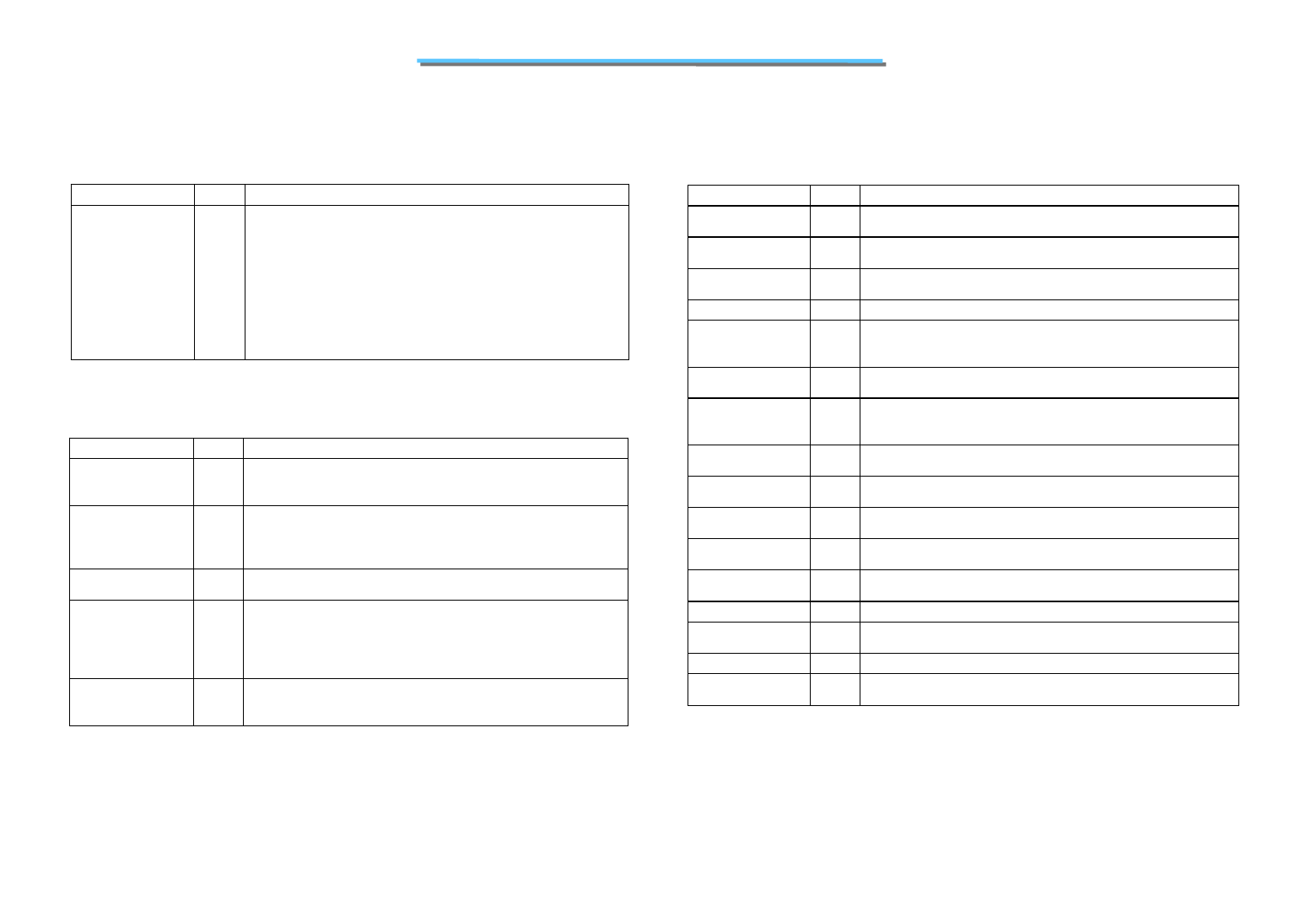

AGP/PCISignals

Name Type Description

G_PAR

I/O

AGP

Parity:

During FRAME# Operations: This signal is driven by the MCH

when it acts as a FRAME#-based AGP initiator during address and

data phases for a write cycle, and during the address phase for a read

cycle. PAR is driven by the MCH when it acts as a FRAME#-based

AGP target during each data phase of a FRAME#-based AGP

memory read cycle. Even parity is generated across AD[31:0] and

G_C/BE[3:0]#.

During SBA and PIPE# Operation: This signal is not used during

SBA and PIPE# operation.

Clocks, Reset, and Miscellaneous Signals

Name Type Description

BCLK

BCLK#

I

CMOS

Differential Host Clock In: These pins receive a differential host

clock from the external clock synthesizer. This clock is used by all of

the MCH logic that is in the host clock domain.

66IN

I

CMOS

66 MHz Clock In: This pin receives a 66 MHz clock from the clock

synthesizer. This clock is used by AGP/PCI and hub interface clock

domains.

Note: That this clock input is 3.3 V tolerant.

SCK[11:0]

O

CMOS

System Memory Clocks (SDR): These signals deliver a

synchronized clock to the DIMMs. There are two per row.

RSTIN#

I

CMOS

Reset In: When asserted, this signal asynchronously resets the MCH

logic. RSTIN# is connected to the PCIRST# output of the ICH2. All

AGP/PCI output and bi-directional signals will also three-state

compliant to PCI Rev 2.0 and 2.1 specifications.

Note: This input needs to be 3.3 V tolerant.

TESTIN#

I

CMOS

Test Input: This pin is used for manufacturing and board level test

purposes.

Note: This signal has an internal pull-up resistor.

Voltage Reference and Power Signals

Name Type Description

HVREF

Ref

Host Reference Voltage: Reference voltage input for the data,

address, and common clock signals of the host AGTL+ interface.

SDREF

Ref

SDRAM Reference Voltage: Reference voltage input for DQ, DQS,

RDCLKIN (SDR).

HI_REF

Ref Hub Interface Reference: Reference voltage input for the hub

interface.

AGPREF

Ref AGP Reference: Reference voltage input for the AGP interface.

HLRCOMP

I/O

CMOS

Compensation for Hub Interface: This signal is used to calibrate

the hub interface I/O buffers. It is connected to a 40.2 . pull-up

resistor with 1% tolerance and is pulled up to VCC1_8.

GRCOMP

I/O

CMOS

Compensation for AGP: This signal is used to calibrate buffers. It is

connected to a 40.2 . pull-down resistor with a 1% tolerance.

HRCOMP[1:0]

I/O

CMOS

Compensation for Host: These signals are used to calibrate the host

AGTL+ I/O buffers. Each signal is connected to a 24.9 . pull-down

resistor with a 1% tolerance.

HSWNG[1:0]

I

CMOS

Host Reference Voltage: Reference voltage input for the

compensation logic.

SMRCOMP

I/O

CMOS

System Memory RCOMP:

VCC1_5

1.5 V Power Input: These pins are connected to a 1.5 V power

source.

VCC1_8

1.8 V Power Input Pins: These pins are connected to a 1.8 V power

source.

VCCSM

SDRAM Power Input Pins: These pins are connected to a 3.3 V

power source for SDR.

VCCA[1:0]

PLL Power Input Pins: These pins provide power for the PLL.

VTT

AGTL+ Bus Termination Voltage Inputs: These pins provide the

AGTL+ bus termination.

VSS

Ground: The VSS pins are the ground pins for the MCH.

VSSA[1:0]

PLL Ground: The VSSA[1:0] pins are the ground pins for the PLL

on the MCH.