127

8170 N/B MAINTENANCE

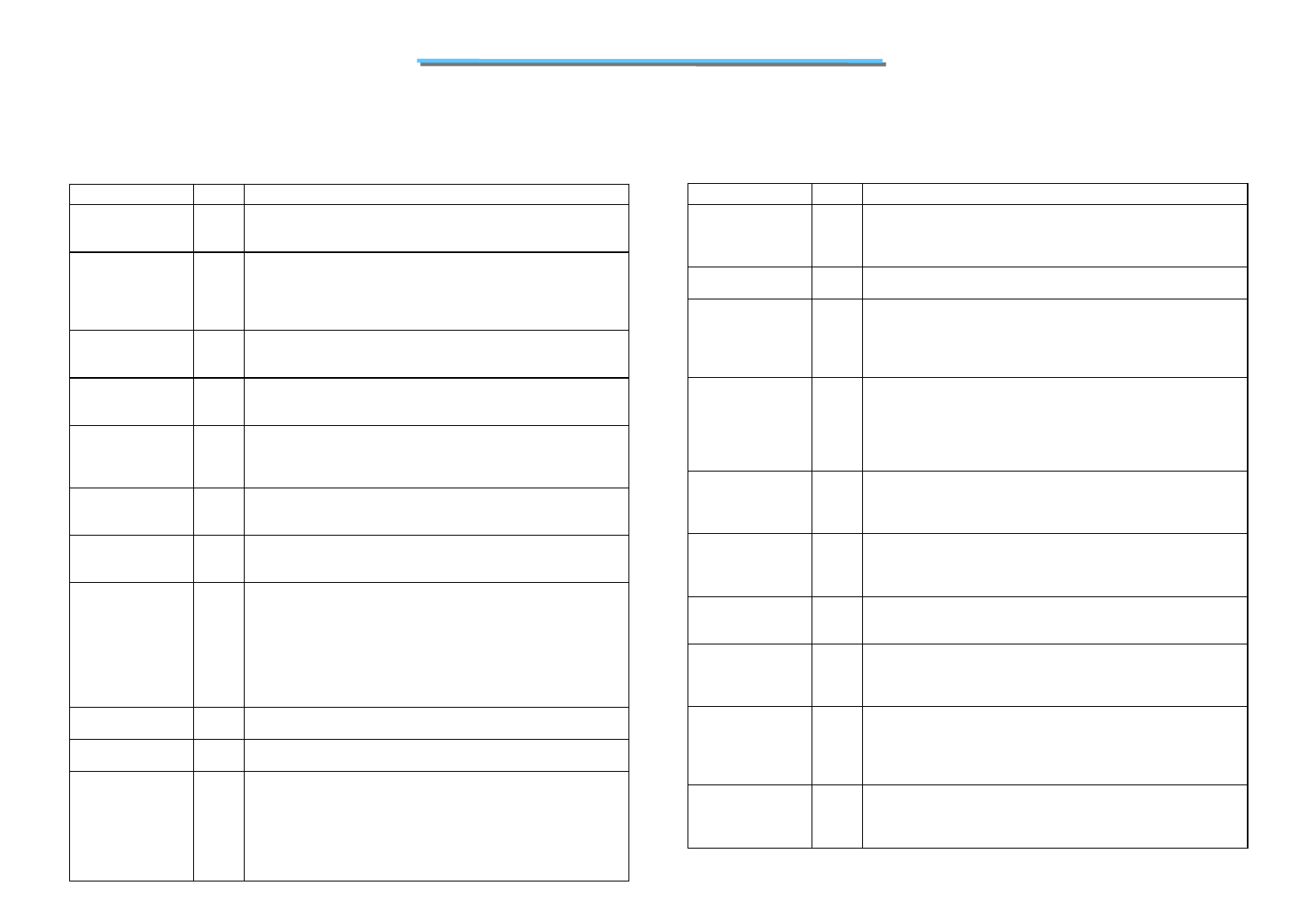

5.3 Intel 82801BA(I/O Controller HUB )

Power Management Interface Signals

Name Type Description

THRM#

I

Thermal Alarm: THRM# is an active low signal generated by

external hardware to start the hardware clock throttling mode. This

signal can also generate an SMI# or an SCI.

SLP_S1#

(ICH2-M only)

O

S1 Sleep Control: Clock synthesizer or power plane control. This

signal connects to clock synthesizer’s PWRDWN# signal. An

optional use is to shut off power to non-critical systems when in the

S1 (Powered On Suspend), S3 (Suspend To RAM), S4 (Suspend to

Disk), or S5 (Soft Off) states.

SLP_S3#

O

S3 Sleep Control: Power plane control. This signal is used to shut off

power to all non-critical systems when in S3 (Suspend To RAM), S4

(Suspend to Disk) or S5 (Soft Off) states.

SLP_S5#

O S5 Sleep Control: Power plane control. This signal is used to shut

power off to all non-critical systems when in the S4 (Suspend To

Disk) or S5 (Soft Off) states.

PWROK

I Power OK: When asserted, PWROK is an indication to the ICH2

that core power and PCICLK have been stable for at least 1 ms.

PWROK can be driven asynchronously. When PWROK is negated,

the ICH2 asserts PCIRST#.

RSM_PWROK

(ICH2 0nly)

I Resume Well Power OK: When asserted, this signal is an indication

to the ICH2 that the resume well power (VccSus3_3, VccSus1_8) has

been stable for at least10 ms.

LAN_PWROK

(ICH2-M only)

I LAN Power OK: When asserted, this signal is an indication to the

ICH2-M that the LAN Controller power (VccLAN3_3, VccLAN1_8)

has been stable for at least 10 ms.

PWRBTN#

I Power Button: The Power Button will cause SMI# or SCI to indicate

a system request to go to a sleep state. If the system is already in a

sleep state, this signal will cause a wake event. If PWRBTN# is

pressed for more than 4 seconds, this will cause an unconditional

transition (power button override) to the S5 state with only the

PWRBTN# available as a wake event. Override will occur even if the

system is in the S1-S4 states. This signal has an internal pull-up

resistor.

RI#

I Ring Indicate: From the modem interface. This signal can be enabled

as a wake event; this is preserved across power failures.

RSMRST#

I Resume Well Reset: RSMRST# is used for resetting the resume

power plane logic.

SUS_STAT# /

LPCPD#

O Suspend Status: This signal is asserted by the ICH2 to indicate that

the system will be entering a low power state soon. This can be

monitored by devices with memory that need to switch from normal

refresh to suspend refresh mode. It can also be used by other

peripherals as an indication that they should isolate their outputs that

may be going to powered-off planes. This signal is called LPCPD# on

the LPC interface.

Name Type Description

C3_STAT# /

GPIO[21]

ICH2-M only)

O

C3_STAT#: This ICH2-M signal is typically configured as

C3_STAT#. It is used for indicating to an AGP device that a C3 state

transition is beginning or ending. If C3_STAT# functionality is not

required, this signal can be used as a GPO.

SUSCLK

O

Suspend Clock: This signal is an output of the RTC generator circuit

and is used by other chips for the refresh clock.

VRMPWRGD

(ICH2)

VRMPWRGD/

VGATE

(ICH2-M)

I

VRM Power Good (ICH2 and ICH2-M): VRMPWRGD should be

connected to be the processor’s VRM Power Good.

VGATE /

VRMPWRGD

(ICH2-M only)

I VRM Power Good Gate (ICH2-M): VGATE is used for Intel®

SpeedStepTM technology support. It is an output from the

processor’s voltage regulator to indicate that the voltage is stable.

This signal can go inactive during a Intel® SpeedStepTM transition.

In non-Intel® SpeedStepTM technology systems this

signal should be connected to the processor VRM Power Good.

AGPBUSY#

(ICH2-M only)

I AGP Bus Busy: This signal supports the C3 state. It provides an

indication that the AGP device is busy. When this signal is asserted,

the BM_STS bit will be set. If this functionality is not needed, this

signal may be configured as a GPI.

STP_PCI#

(ICH2-M only)

O Stop PCI Clock: This signal is an output to the external clock

generator to turn off the PCI clock. It is used to support PCI

CLKRUN# protocol. If this functionality is not needed, this signal

can be configured as a GPO.

STP_CPU#

(ICH2-M only)

O Stop CPU Clock: Output to the external clock generator to turn off

the processor clock. It is used to support the C3 state. If this

functionality is not needed, this signal can be configured as a GPO.

BATLOW#

(ICH2-M only)

I Battery Low: Input from battery to indicate that there is insufficient

power to boot the system. Assertion prevents wake from S1–S5 state.

This signal can also be enabled to cause an SMI# when asserted. In

desktop configurations this signal should be pulled high to VccSUS.

CPUPERF#

(ICH2-M only)

OD CPU Performance: This signal is used for Intel® SpeedStepTM

technology support. It selects which power state to put the processo

in. If this functionality is not needed, this signal can be configured as

a GPO. This is an open-drain output signal and requires an external

pull-up to the processor I/O voltage.

SSMUXSEL

(ICH2-M only)

O SpeedStep Mux Select: This signal is used for Intel SpeedStepTM

technology support. It selects the voltage level for the processor. If

this functionality is not needed, this signal can be configured as a

GPO.