126

8170 N/B MAINTENANCE

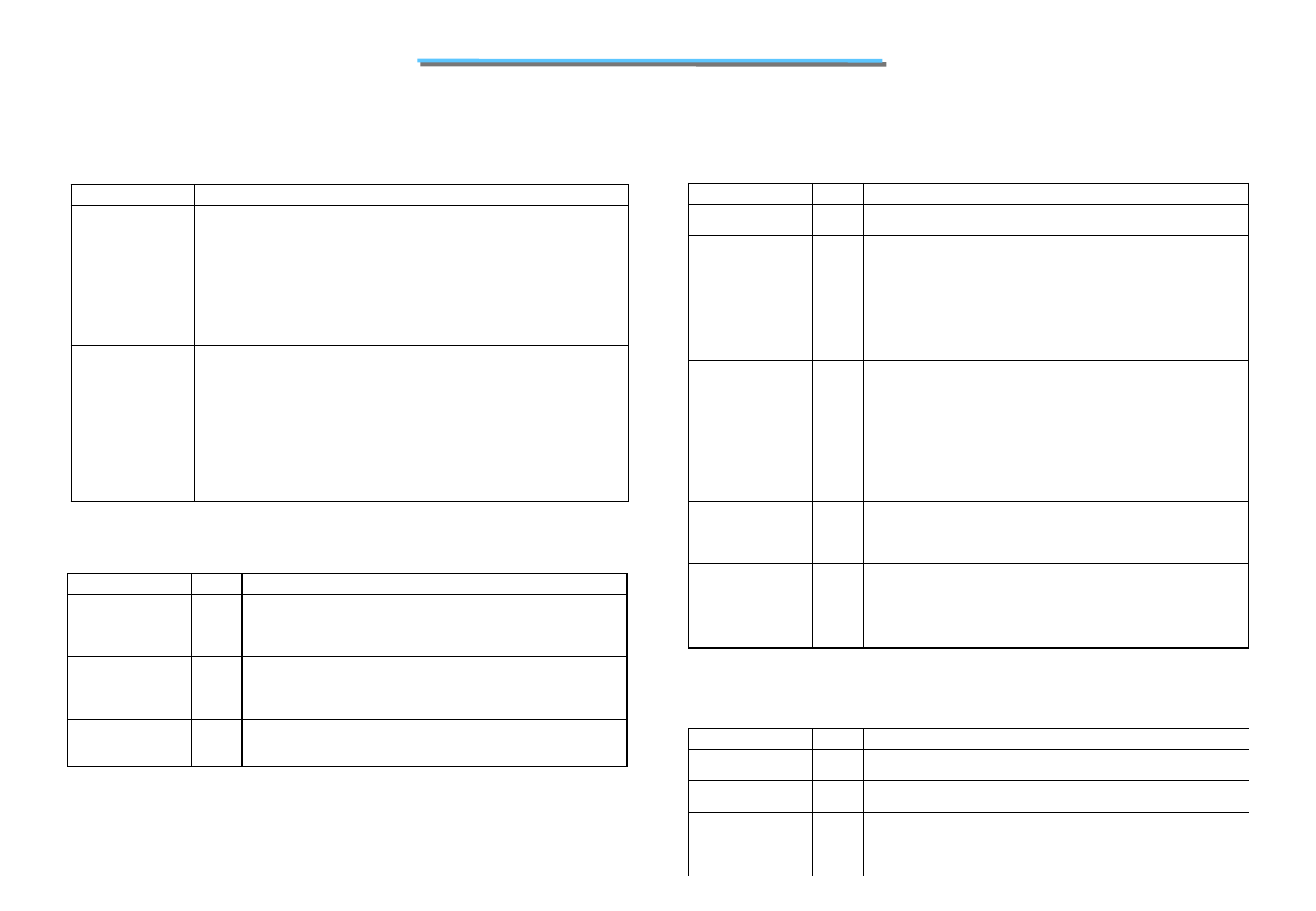

5.3 Intel 82801BA(I/O Controller HUB )

IDE Interface Signals(continued)

Name Type Description

PDIOW#

SDIOW#

O

Primary and Secondary Disk I/O Write (PIO and Non-Ultra

DMA): This is the command to the IDE device that it may latch data

from the PDD or SDD lines. Data is latched by the IDE device on the

deassertion edge of PDIOW# or SDIOW#. The IDE device is selected

either by the ATA register file chip selects (PDCS1# or SDCS1#,

PDCS3# or SDCS3#) and the PDA or SDA lines, or the IDE DMA

acknowledge (PDDAK# or SDDAK#).

Primary and Secondary Disk Stop (Ultra DMA): ICH2 asserts this

signal to terminate a burst.

PIORDY

SIORDY

I Primary and Secondary I/O Channel Ready (PIO): This signal

keeps the strobe active (PDIOR# or SDIOR# on reads, PDIOW# or

SDIOW# on writes) longer than the minimum width. It adds wait

states to PIO transfers.

Primary and Secondary Disk Read Strobe (Ultra DMA Reads

from Disk): When reading from disk, ICH2 latches data on rising and

falling edges of this signal from the disk.

Primary and Secondary Disk DMA Ready (Ultra DMA Writes to

Disk): When writing to disk, this is deasserted by the disk to pause

burst data transfers

LPC Interface Signals

Name Type Description

LAD[3:0] /

FWH[3:0]

I/O LPC Multiplexed Command, Address, Data: Internal pull-ups are

provided.

LFRAME# /

FWH[4]

O LPC Frame: LFRAME# indicates the start of an LPC cycle, or an

abort.

LDRQ[1:0]#

O LPC Serial DMA/Master Request Inputs: These signals are used to

request DMA or bus master access. Typically, they are connected to

external Super I/O device. An internal pull-up resistor is provided on

these signals.

Interrupt Signals

Name Type Description

SERIRQ

I/O Serial Interrupt Request: This pin implements the serial interrupt

protocol.

PIRQ[D:A]#

I/OD

PCI Interrupt Requests: In Non-APIC Mode the PIRQx# signals

can be routed to interrupts 3:7, 9:12, 14, or 15 as described in the

Interrupt Steering section. Each PIRQx# line has a separate Route

Control Register.

In APIC mode, these signals are connected to the internal I/O APIC in

the following fashion: PIRQ[A]# is connected to IRQ16, PIRQ[B]# to

IRQ17, PIRQ[C]# to IRQ18, and PIRQ[D]# to IRQ19. This frees the

ISA interrupts.

PIRQ[H]#,

PIRQ[G:F]#

GPIO[4:3],

PIRQ[E]#

I/OD

PCI Interrupt Requests: In Non-APIC Mode the PIRQx# signals

can be routed to interrupts 3:7, 9:12, 14 or 15 as described in the

Interrupt Steering section. Each PIRQx# line has a separate Route

Control Register.

In APIC mode, these signals are connected to the internal I/O APIC in

the following fashion: PIRQ[E]# is connected to IRQ20, PIRQ[F]# to

IRQ21, PIRQ[G]# to IRQ22, and PIRQ[H]# to IRQ23. This frees the

ISA interrupts. If not needed for interrupts, PIRQ[G:F] can be used as

GPIO.

IRQ[14:15]

I Interrupt Request 14:15: These interrupt inputs are connected to the

IDE drives. IRQ14 is used by the drives connected to the primary

controller and IRQ15 is used

b

y the drives connected to the secondary

controller.

APICCLK I APIC Clock: The APIC clock runs at 33.333 MHz.

APICD[1:0]

I/OD

APIC Data: These bi-directional open drain signals are used to send

and receive data over the APIC bus. As in

p

uts, the data is valid on the

rising edge of APICCLK.As outputs, new data is driven from the

rising edge of the APICCLK.

USB Interface Signals

Name Type Description

USBP0P,

USBP0N,

USBP1P,

USBP1N

I/O

Universal Serial Bus Port 1:0 Differential: These differential pairs

are used to transmit Data/Address/Command signals for ports 0 and 1

(USB Controller 1).

USBP2P,

USBP2N,

USBP3P,

USBP3N

I/O

Universal Serial Bus Port 3:2 Differential: These differential pairs

are used to transmit Data/Address/Command signals for ports 2 and 3

USB Controller 2).

OC[3:0]#

I

Overcurrent Indicators: These signals set corresponding bits in the

USB controllers to indicate that an overcurrent condition has

occurred.