7 - 24 7 - 24

MELSEC-Q

7 DATA COMMUNICATIONS USING BIDIRECTIONAL PROTOCOL

7.3 Processing when Simultaneous Transmission Performed During Full-Duplex

Communications

This section explains the processing when simultaneous transmissions occur in full-

duplex communication.

7.3.1 Processing when simultaneous transmissions occur

This section explains the processing performed by the Q series C24 when the external

device and the Q series C24 transmit at the same time during data communications

using the bidirectional protocol.

Since the external device and the Q series C24 do not transmit at the same time

during half-duplex communications (see User's Manual (Application) Chapter 8), this

section does not have to be read.

When an external device and the Q series C24 transmit at the same time, the Q series

C24 processing depends on the setting of "Simultaneous transmission data valid/invalid

designation" with GX Configurator-SC.

The GX Configurator-SC setting value, "Simultaneous transmission data valid/invalid

designation" is stored in the following areas of the buffer memory.

Simultaneous transmission data valid/invalid designation area (addresses: 9B

H

/13B

H

)

The Q series C24 communication data processing for each setting is described in

Section 7.3.2.

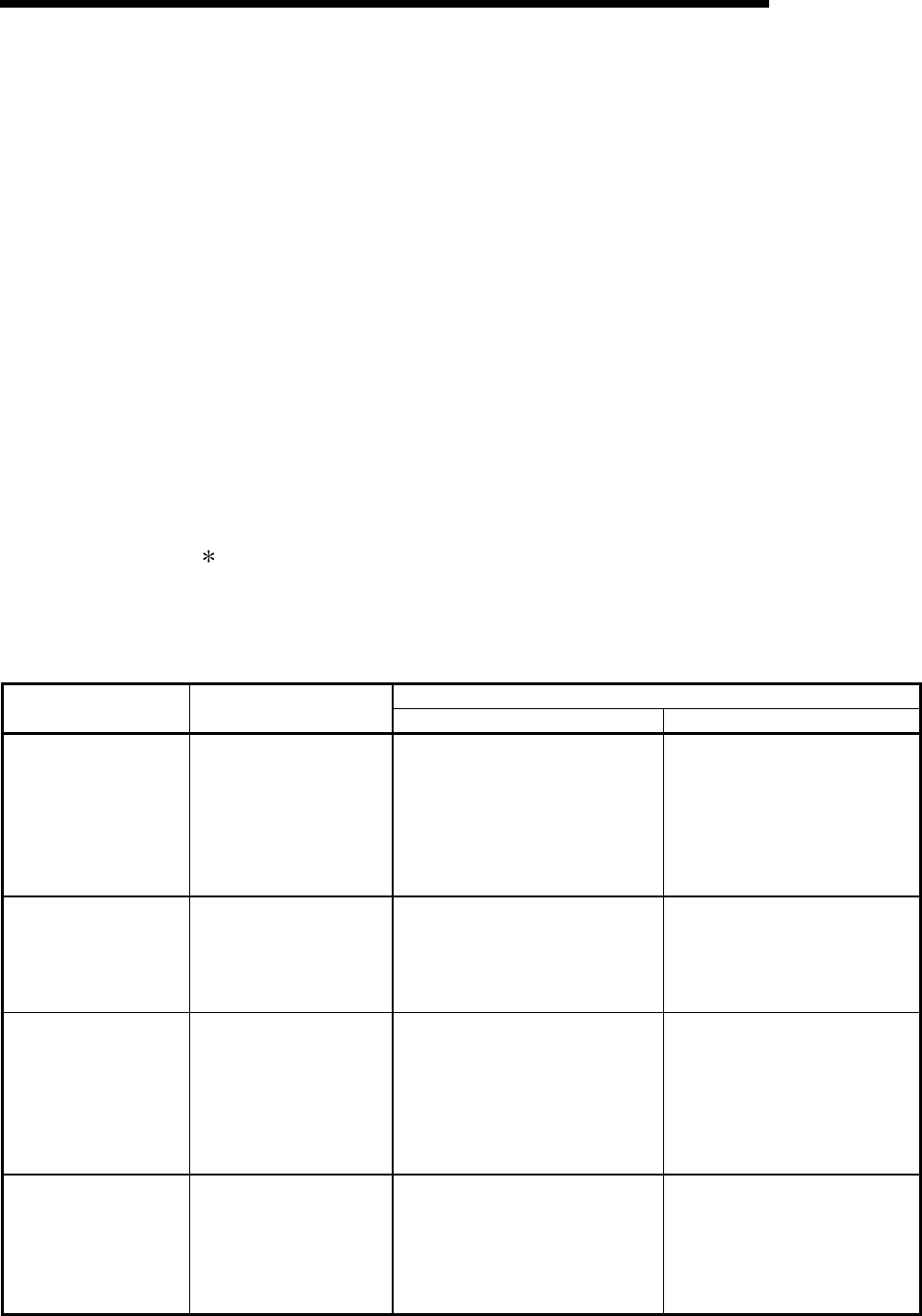

Q series C24 processing contents

Setting contents

with GX Configurator-SC

Value set to buffer memory

(Address 9B

H

/13B

H

)

Message transmit processing Message receive processing

Transmission data: Valid

Receive data: Valid

0000

H

Waits to receive the response message

(1)-2) while checking time-out after data

transmission (1)-1) is complete.

Posts normal end or abnormal end

according to whether or not the PLC

CPU received a response message

through the buffer memory.

Transmits a response message (2)-2)

after data reception (2)-1) is complete.

Posts the receive data and receive

result to the PLC CPU through the

buffer memory.

Transmission data: Invalid

Receive data: Valid

0100

H

Posts a simultaneous transmission error

to the PLC CPU through the buffer

memory after data transmission (1)-1).

Does not wait for a response massage

(1)-2) in reply to data transmission (1)-1).

Transmits a response message (2)-2)

after data reception (2)-1) is complete.

Posts the receive data and receive

result to the PLC CPU through the

buffer memory.

Transmission data: Valid

Receive data: Invalid

0001

H

Waits to receive the response message

(1)-2) while checking time-out after data

transmission (1)-1) is complete.

Posts normal end or abnormal end

according to whether or not the PLC

CPU received a response message

through the buffer memory.

Ignores data reception (2)-1) and

discards the received data.

Does not transmit a response

message (2)-2).

Does not inform the PLC CPU that

data was received.

Transmission data: Invalid

Receive data: Invalid

0101

H

Posts a simultaneous transmission error

to the PLC CPU through the buffer

memory after data transmission (1)-1).

Does not wait to a response massage

(1)-2) in reply to data transmission (1)-1).

Ignored data reception (2)-1) and

discards the receive data.

Does not transmit a response

message (2)-2).

Does not inform the PLC CPU that

data was received.

( )-m) is the number showing the correspondence with the messages in the illustration shown in Section 7.3.2.