TNETX4090

ThunderSWITCH II

9-PORT 100-/1000-MBIT/S ETHERNET

SWITCH

SPWS044E – DECEMBER 1997 – REVISED AUGUST 1999

13

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

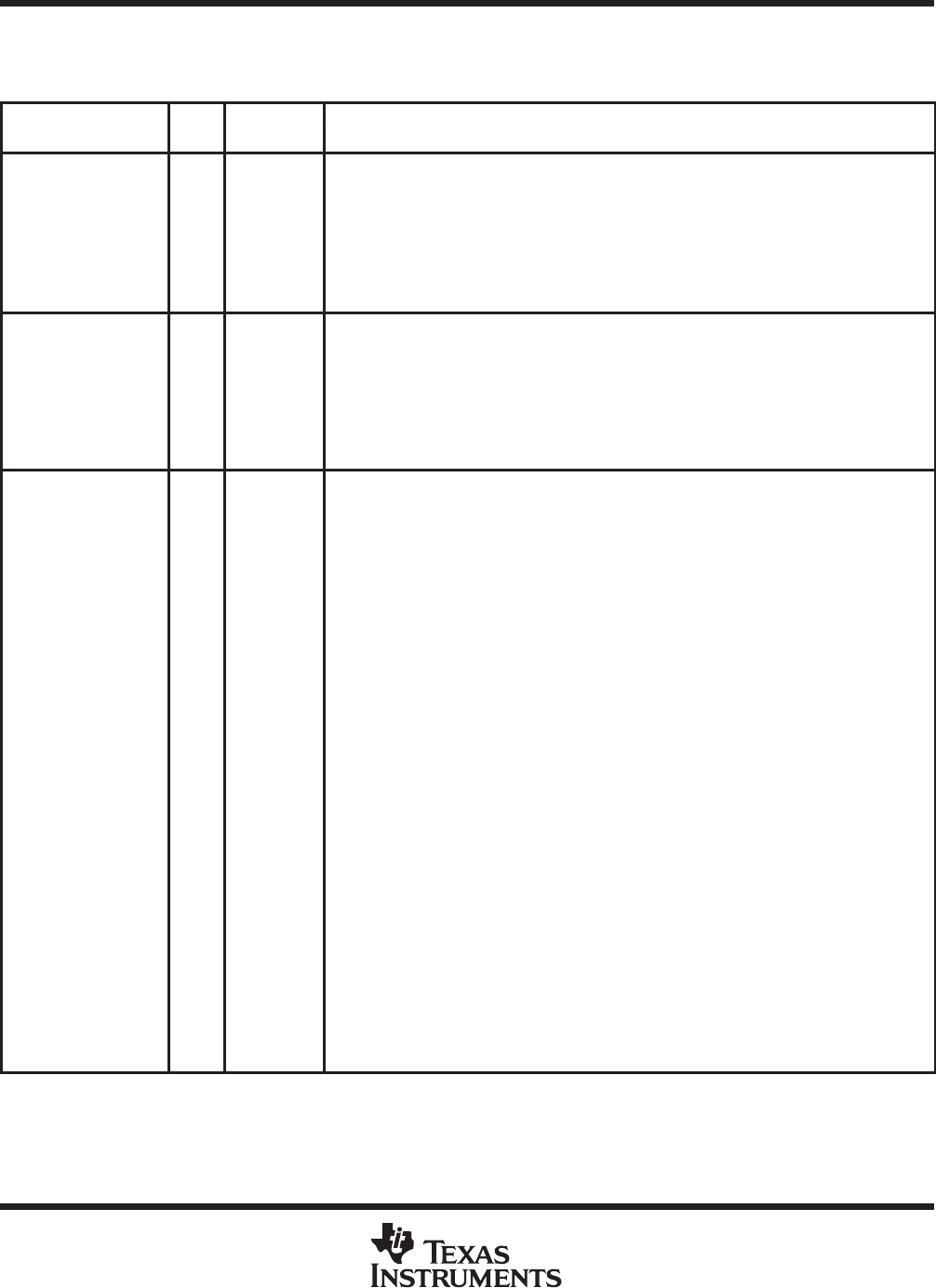

Terminal Functions (Continued)

10-/100-Mbit/s MAC interface (MII mode) (ports 0–7) (continued)

TERMINAL

I/O

INTERNAL

DESCRIPTION

NAME NO.

I/O

RESISTOR

DESCRIPTION

M00_RXER

M01_RXER

M02_RXER

M03_RXER

M04_RXER

M05_RXER

M06_RXER

M07_RXER

C19

C14

B9

B4

L4

T3

AA2

AD8

I Pulldown Receive error. Indicates reception of a coding error on received data.

M00_TCLK

M01_TCLK

M02_TCLK

M03_TCLK

M04_TCLK

M05_TCLK

M06_TCLK

M07_TCLK

B23

C17

C13

A8

F1

L2

T1

AD4

I Pullup Transmit clock. Transmit clock source from the attached PHY or PMI device.

M00_TXD3

M00_TXD2

M00_TXD1

M00_TXD0

M01_TXD3

M01_TXD2

M01_TXD1

M01_TXD0

M02_TXD3

M02_TXD2

M02_TXD1

M02_TXD0

M03_TXD3

M03_TXD2

M03_TXD1

M03_TXD0

M04_TXD3

M04_TXD2

M04_TXD1

M04_TXD0

M05_TXD3

M05_TXD2

M05_TXD1

M05_TXD0

M06_TXD3

M06_TXD2

M06_TXD1

M06_TXD0

M07_TXD3

M07_TXD2

M07_TXD1

M07_TXD0

C22

B22

A22

A23

C18

B18

A18

A19

D12

C12

B12

A12

D7

C7

B7

A7

G4

G3

G2

G1

M4

M3

M2

M1

U4

U3

U2

U1

AC5

AD5

AE5

AF5

O None

Transmit data. Byte transmit data. When Mxx_TXEN is asserted, these signals carry

transmit data. Data on these signals is synchronous to Mxx_TCLK. When Mxx_TXEN,

Mxx_TXER, and Mxx_LINK are all low, these terminals indicate the desired capabilities for

autonegotiation as follows:

– Mxx_TXD0 indicates full-duplex capability when high; half duplex when low, as

determined by reqhd in PortxControl.

– Mxx_TXD1 indicates IEEE Std 802.3 pause frame support when high; no pause

when low, as determined by reqnp in PortxControl.

– Mxx_TXD2 indicates 100 Mbit/s when high; 10 Mbit/s when low, as determined by

req10 in PortxControl.

– Mxx_TXD3 is unused and is 0.