TNETX4090

ThunderSWITCH II

9-PORT 100-/1000-MBIT/S ETHERNET

SWITCH

SPWS044E – DECEMBER 1997 – REVISED AUGUST 1999

62

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

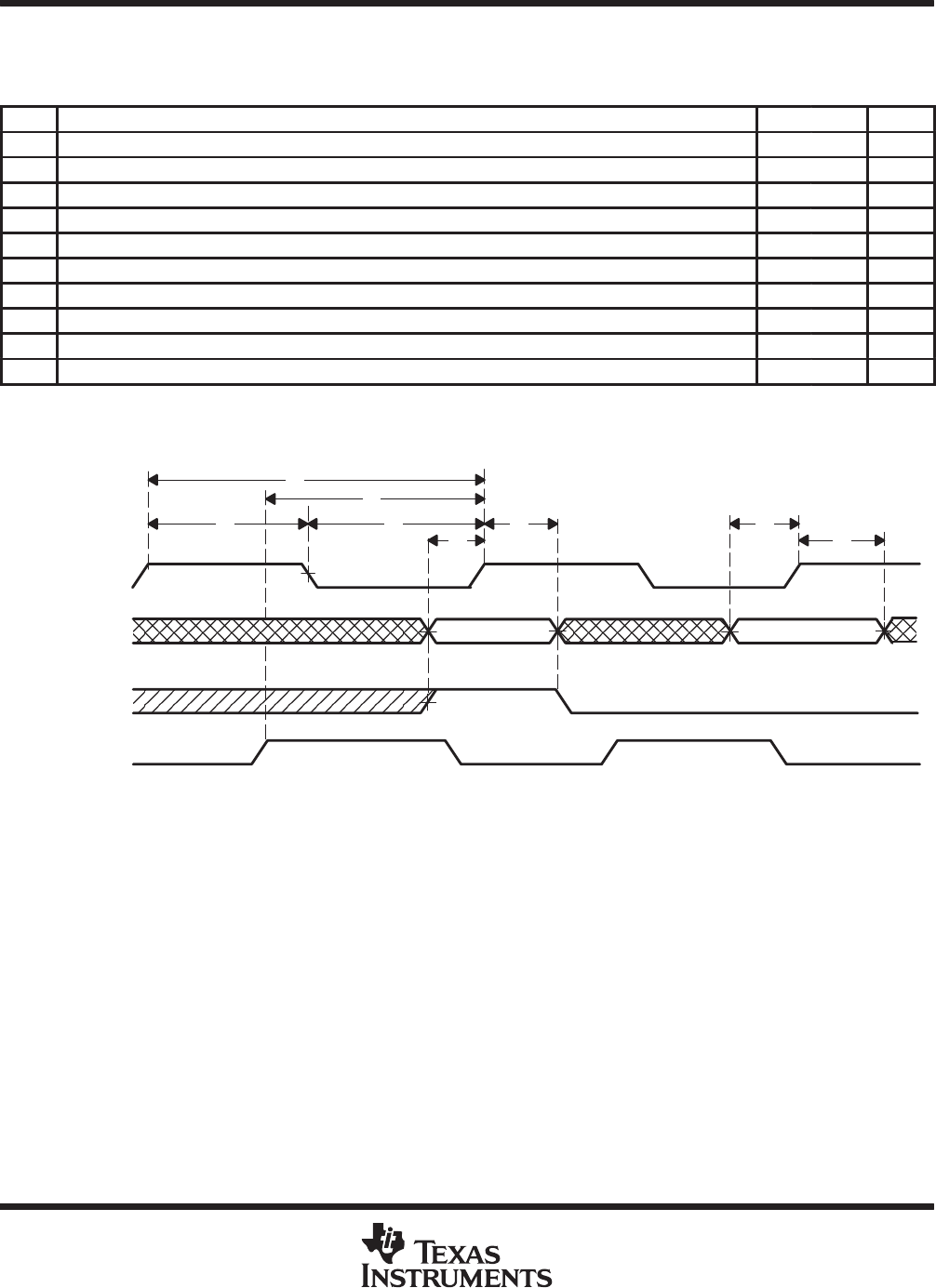

physical medium attachment interface (port 8)

receive

PMA receive (see Figure 16)

NO. MIN MAX UNIT

1 t

c(Mxx_RBC)

Cycle time, receive byte clock 0 and 1 (Mxx_RCLK, Mxx_COL) 16 16 ns

– t

drift(Mxx_RBC)

Drift rate

†

of receive bye clock 0 and 1 0.2 ns

2,3 t

w(Mxx_RBC)

Pulse duration, Mxx_RCLK, Mxx_COL low or high 40% 60% ns

4 t

su(Mxx_RXD)

Setup time, Mxx_RXD7–Mxx_RXD0 valid before Mxx_RCLK/COL↑ 2.5 ns

4 t

su(Mxx_RXDV)

Setup time, Mxx_RXDV valid before Mxx_RCLK/COL↑ 2.5 ns

4 t

su(Mxx_RXER)

Setup time, Mxx_RXER valid before Mxx_RCLK/COL↑ 2.5 ns

5 t

h(Mxx_RXD)

Hold time, Mxx_RXD7–Mxx_RXD0 valid after Mxx_RCLK/COL↑ 1.5 ns

5 t

h(Mxx_RXDV)

Hold time, Mxx_RXDV valid after Mxx_RCLK/COL↑ 1.5 ns

5 t

h(Mxx_RXER)

Hold time, Mxx_RXER valid after Mxx_RCLK/COL↑ 1.5 ns

6 t

skew(Mxx_RBC)

Skew between receive byte clock 1 and receive byte clock 0 7.5 8.5 ns

†

t

drift

is the (minimum) time for either RBC0 or RBC1 to drift from 63.5 MHz to 64.5 MHz or 60 Mhz to 59 MHz from their lock value. It is applicable

under all input signal conditions (except under certain circumstances during comma detection), including invalid or absent input signals, if the

receiver clock recovery unit was previously locked to Mxx_RFCLK or to a valid input signal.

Receive Byte

Clock 0

Data Group

1

6

2 5

4

4

5

Comma Detect

Receive

Code Group

Receive Byte

Clock 0

3

Figure 16. PMA Receive