TNETX4090

ThunderSWITCH II

9-PORT 100-/1000-MBIT/S ETHERNET

SWITCH

SPWS044E – DECEMBER 1997 – REVISED AUGUST 1999

36

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

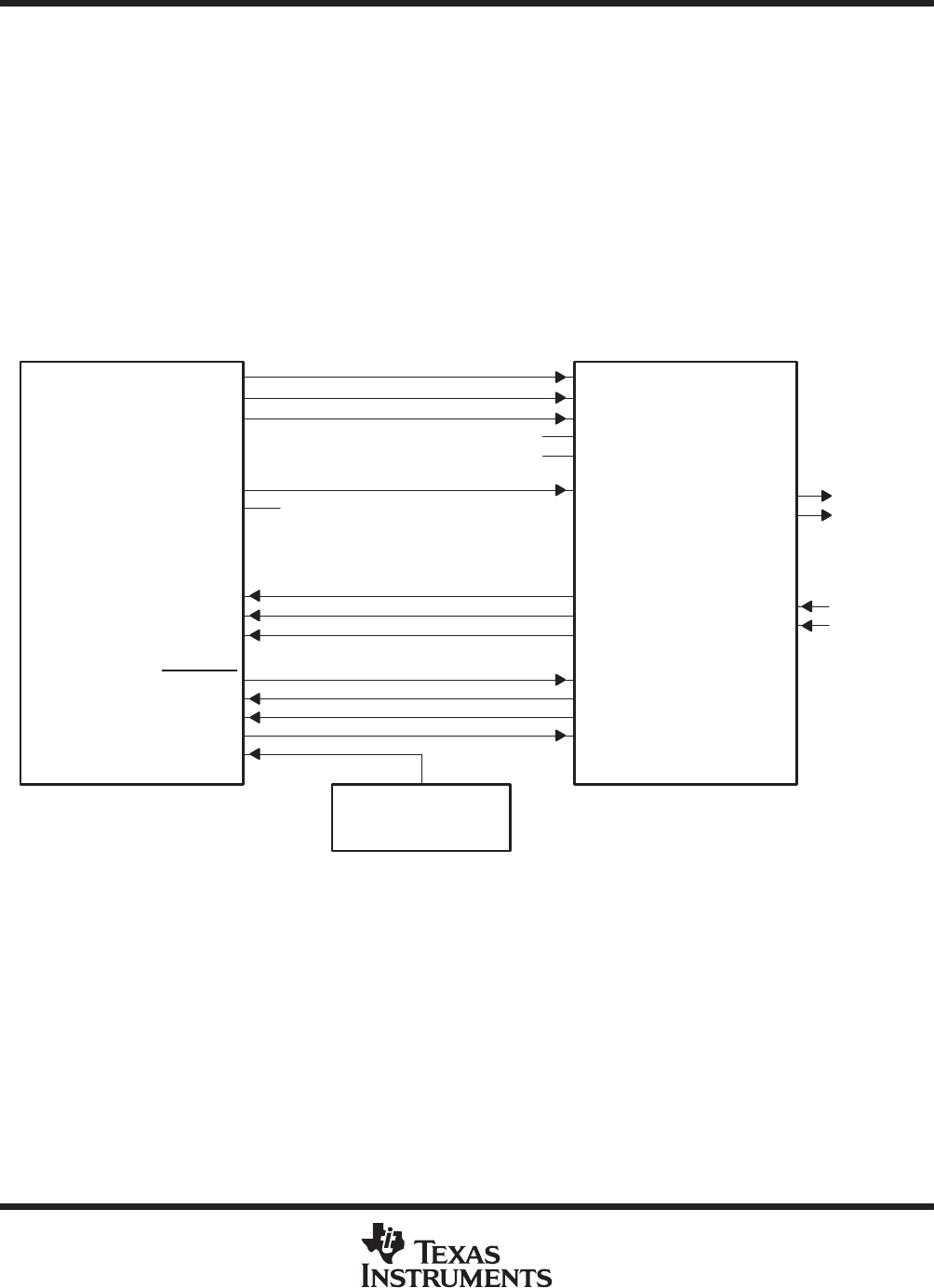

100-/1000-Mbit/s PHY interface (port 8)

This port is controlled by an IEEE Std 802.3-compliant MAC.

speed, duplex, and flow-control negotiation

When in PMA mode and autonegotiation is enabled, the on-chip PCS layer attempts to establish a compatible

mode of operation with the attached serializer/deserializer (SERDES).

If manual override has been established, no autonegotiation takes place and the interface mode of operation

is determined by the values in Port8Control.

The PCS layer may be forced to start autonegotiation by writing a 0 and then a 1 to the neg bit in Port8Control,

but, alternatively, you could hit the newaneg bit in PCS8Control.

Figure 4 shows how the gigabit port on the TNETX4090 can be connected to a SERDES device. Table 1 gives

a description of the device terminals.

M08_RXD0–M08_RXD7

Tie to Signal Detect Terminal of

Optical Receiver, SERDES Device,

or to V

CC

Serial Data

Output

Serial Data

Input

M08_TXD0–M08_TXD7

M08_TXEN

M08_TXER

TD0–TD7

TD8

TD9

SYNCNC

V

CC

SYNCEN

M08_EWRAP

M08_LINK

TNETX4090

Gigabit Port Terminals

TNETE2201

(SERDES Device)

M08_LREF

M08_COL

M08_RCLK

M08_RXDV

M08_RXER

M08_GTCLK

M08_RFCLK

LOOPEN

RD0–RD7

RD8

RD9

DOUT_TXP

DOUT_TXN

DIN_RXP

DIN_RXN

LCKREFN

RBC1

RBC0

RFCLK

125-MHz Clock

NOTE: The SYNC output from the SERDES device is not used by the TNETX4090. The SYNCEN input on the SERDES device must be tied

high (enabled) for proper operation. The M08_LINK terminal on the TNETX4090 must be tied to the signal detect terminal of an attached

optical receiver or tied high if a comparable terminal is unavailable.

Figure 4. TNETX4090 Gigabit Port to SERDES Device Connections