TNETX4090

ThunderSWITCH II

9-PORT 100-/1000-MBIT/S ETHERNET

SWITCH

SPWS044E – DECEMBER 1997 – REVISED AUGUST 1999

68

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

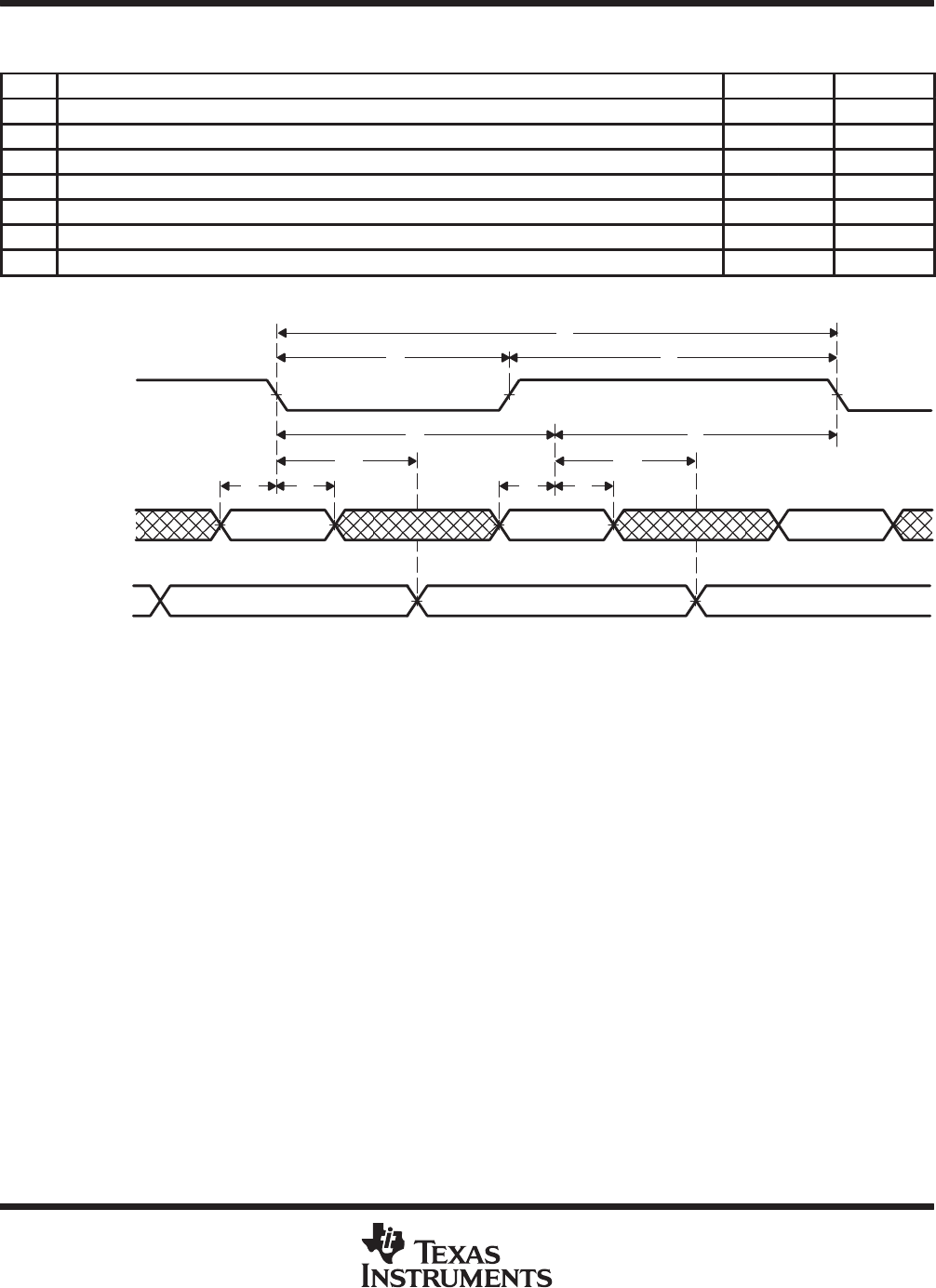

RDRAM interface

RDRAM (see Figure 24)

NO. MIN MAX UNIT

1 t

c(DX_CLK)

Cycle time DTX_CLK, DRX_CLK 3.33 3.33 ns

2, 3 t

w(DX_CLK)

Pulse duration, DTX_CLK, DRX_CLK low or high 45% 55% t

c(DX_CLK)

4, 5 t

w(TICK)

Pulse duration, tick time 0.5 0.5 t

cycle

6, 8 t

su(DBUS_DATA)

Setup time, DBUS_DATA before tick 0.35 ns

7, 9 t

h(DBUS_DATA)

Hold time, DBUS_DATA after tick 0.35 ns

10, 11 t

d(DBUS_OUT)

Delay time, DBUS_DATA, DBUS_CTRL, DBUS_EN from tick 0.635 1.438 t

c(DX_CLK)

t

cycle

†

Cycle time, internal clock 4 t

c(DX_CLK)

†

Not shown in Figure 24 due to scale

DBUS_DATA (in)

DTX_CLK

DRX_CLK

DBUS_CTRL

DBUS_EN

DBUS_DATA (out)

6 7 8 9

10 11

4 5

2 3

1

Figure 24. RDRAM