TNETX4090

ThunderSWITCH II

9-PORT 100-/1000-MBIT/S ETHERNET

SWITCH

SPWS044E – DECEMBER 1997 – REVISED AUGUST 1999

7

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

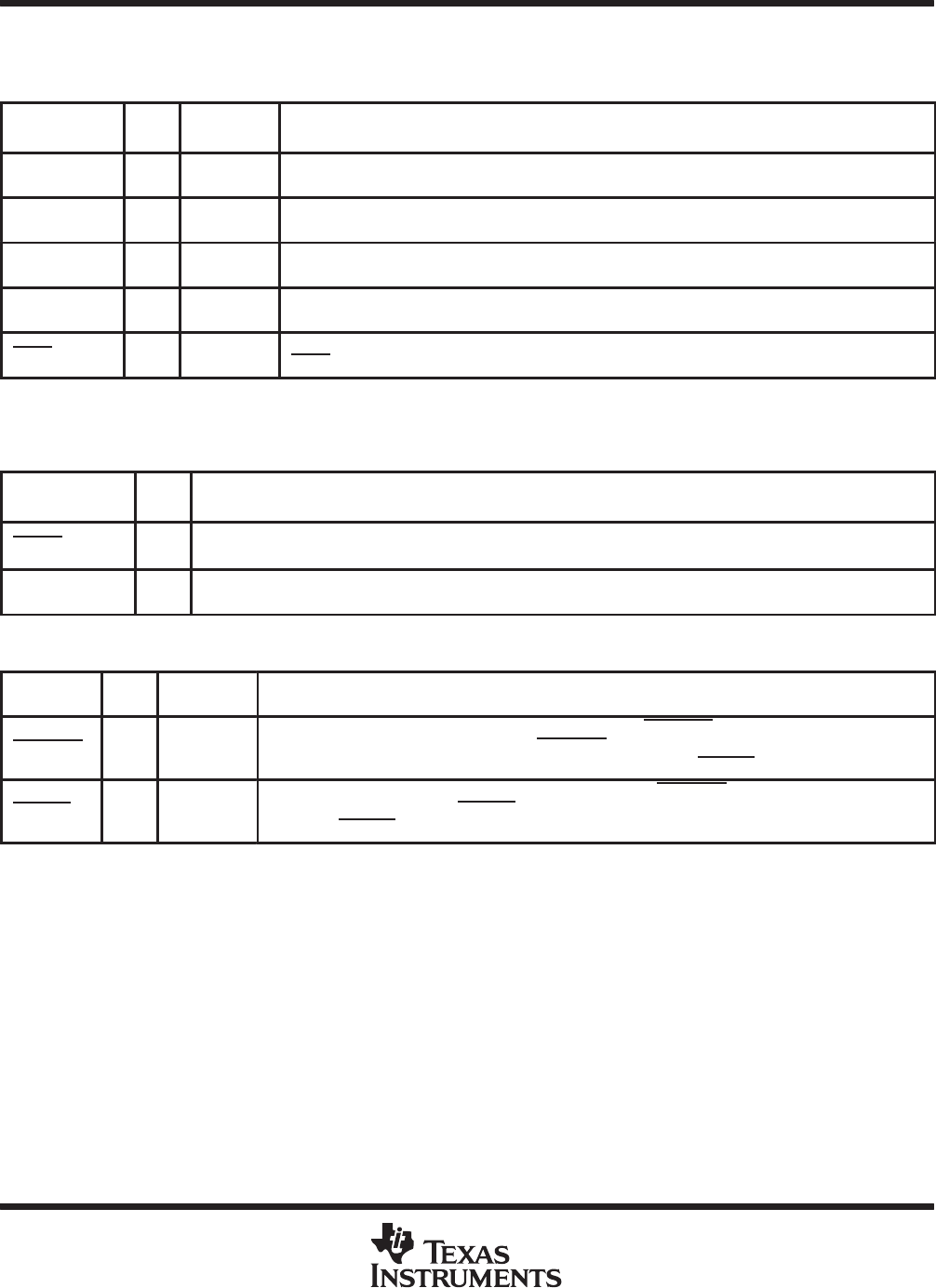

Terminal Functions

JTAG interface

TERMINAL

I/O

INTERNAL

DESCRIPTION

NAME NO.

I/O

RESISTOR

†

DESCRIPTION

TCLK L24

I Pullup

Test clock. Clocks state information and test data into and out of the TNETX4090 during operation

of the test port.

TDI M24

I Pullup

Test data input. Serially shifts test data and test instructions into the TNETX4090 during operation

of the test port. An internal pullup resistor is provided on TDI to ensure JTAG compliance.

TDO L23

O None

Test data out. Serially shifts test data and test instructions out of the TNETX4090 during operation

of the test port.

TMS M25

I Pullup

Test mode select. Controls the state of the test-port controller. An internal pullup resistor is provided

on TMS to ensure JTAG compliance.

TRST L25

I Pullup

Test reset. Asynchronously resets the test-port controller. An internal pullup resistor is provided on

TRST

to ensure JTAG compliance.

†

Internal resistors are provided to pull signals to known values. The system designers should determine if additional pullups or pulldowns are

required in their systems.

control logic interface

TERMINAL

I/O

DESCRIPTION

NAME NO.

I/O

DESCRIPTION

RESET

M23 I

Device reset. Asserted for a minimum of 100 µs after power supplies and clocks have stabilized. The system clock

must be operational during reset.

FLOW

AF8 O

Flow control. When flow control is activated (flow in SysControl = 1) and the number of free external memory

buffers is below the threshold indicated in FlowThreshold, FLOW is asserted.

100-/1000-Mbit/s MAC interface [gigabit media-independent interface (GMII) (port 8)]

TERMINAL

NAME

I/O

INTERNAL

RESISTOR

†

DESCRIPTION

M08_PMA

I Pullup

PMA mode. PMA mode can be selected by either pulling M08_PMA low externally, or by setting the

reqpma bit in the PortxControl register. If M08_PMA

is allowed to float high, the port is configured as

either an MII or GMII interface, as determined by the value of the M08_MII

terminal.

M08_MII

I Pullup

MII or GMII selection. The value of this terminal is ignored if M08_PMA = 0. 100-Mbit/s MII mode can

be selected by either pulling M08_MII

low externally, or by setting the req100 bit in the PortxControl

register. If M08_MII

is allowed to float high, the port is configured as a GMII interface.

†

Internal resistors are provided to pull signals to known values. The system designers should determine if additional pullups or pulldowns are

required in their systems.