Troubleshooting Procedures

2-28 [CONFIDENTIAL] TECRA A11/S11/P11/Satellite Pro S500 Series Maintenance Manual (960-784)

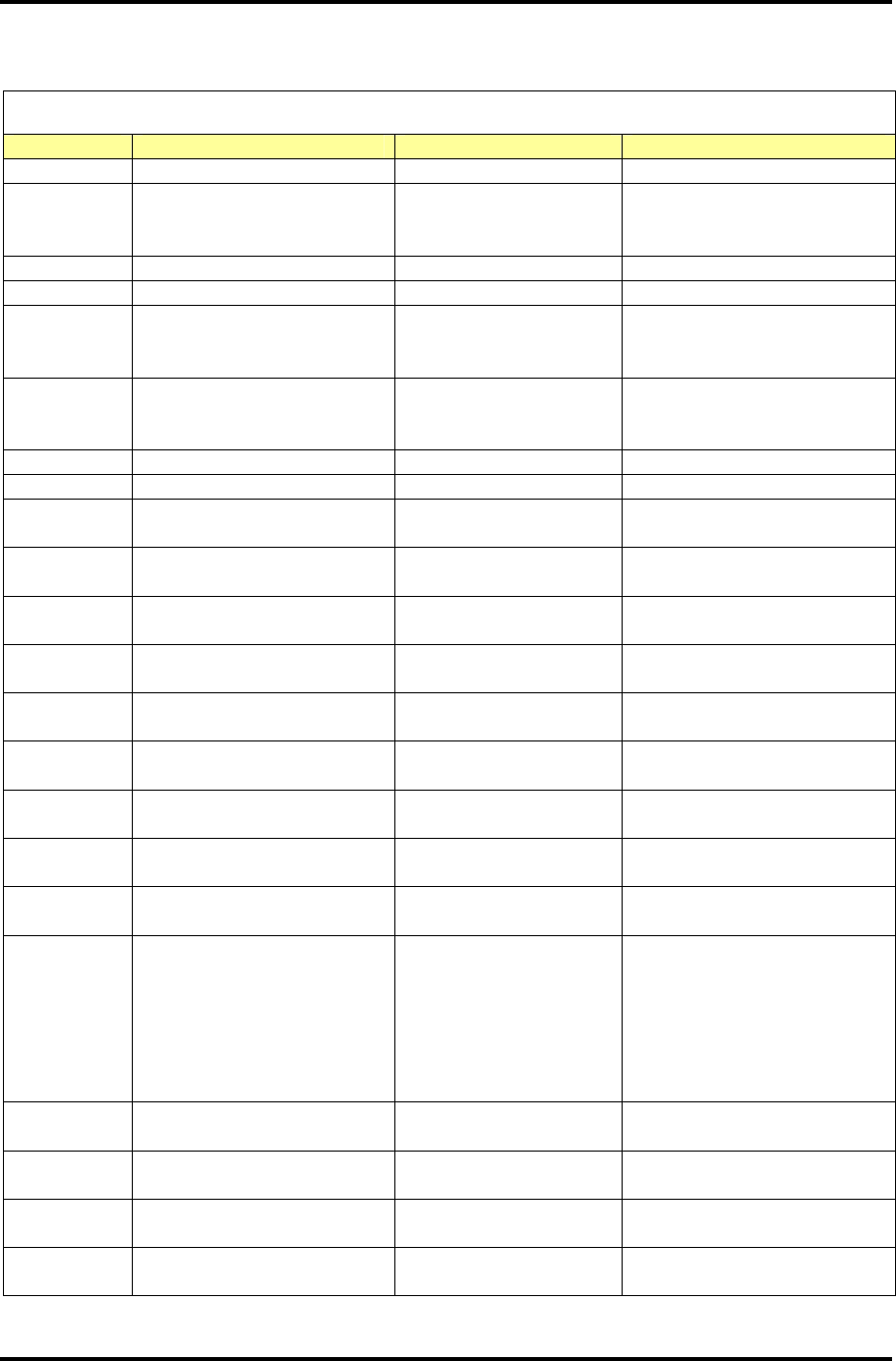

Table 2-4 Debug port error status (2/2)

System BIOS IRT processing

Debug Code BIOS processing outline Target Device IC No.

F100 IRT section start CPU IS1050 (CPU Socket)

F101

Creation of SETUP

information

BIOSROM

RAM

IC3000/IC3002 (BIOS ROM)

CN1400, CN1410 (RAM

Conn.)

F102 PCI Express initialization PCH IC1600 (PCH)

F103 PCH Express initialization PCH IC1600 (PCH)

F104

SMRAM Express

initialization

PCH

RAM

IC1600 (PCH)

CN1400, CN1410 (RAM

Conn.)

F105

End of SMRAM

initialization

PCH

RAM

IS1050 (CPU Socket),

CN1400, CN1410 (RAM

Conn.)

F106 EC Evart initialization EC IC3200 (EC/KBC)

F107 USB Legacy initialization PCH IC1600 (PCH)

F108

Device Lock main

processing start

RAM

CN1400, CN1410 (RAM

Conn.)

F109

Device Lock device

processing start

RAM

CN1400, CN1410 (RAM

Conn.)

F10A

End of Device Lock main

processing

RAM

CN1400, CN1410 (RAM

Conn.)

F10B

Thermal control

initialization

RAM

CN1400, CN1410 (RAM

Conn.)

F10C

Digital thermal sensor

initialization

CPU IS1050 (CPU Socket)

F10D

End for IRT of a module

load

RAM

CN1400, CN1410 (RAM

Conn.)

F10E Memory test start RAM

CN1400, CN1410 (RAM

Conn.)

F10F End of a memory test RAM

CN1400, CN1410 (RAM

Conn.)

F110 Interrupt vector initialization RAM

CN1400, CN1410 (RAM

Conn.)

F111 VGA, LAN initialization

VGA

LAN

BIOSROM

RAM

IC1200 (VGA)

IC5000 (VGA (nVIDIA))

IC4000/IC4100 (LAN

Controller),

IC3000/IC3002 (BIOS

ROM), CN1400, CN1410

(RAM Conn.)

F112

End of option ROM

execution

RAM

CN1400, CN1410 (RAM

Conn.)

F113

Determination of a boot

device

RAM

CN1400, CN1410 (RAM

Conn.)

F114 Processing in front of boot RAM

CN1400, CN1410 (RAM

Conn.)

F115

End of IRT processing.

Shift to OS.

RAM

CN1400, CN1410 (RAM

Conn.)