TMP92CM22

2007-02-16

92CM22-167

Protocol

1. Select 9-bit UART mode on the master and slave controllers.

2. Set the SC0MOD0<WU> bit on each slave controller to 1 to enable data receiving.

3. The master controller transmits one-frame data including the 8-bit select code for

the slave controllers. The MSB (Bit8) <TB8> is set to “1”.

4. Each slave controller receives the above frame. If it matches with own select code,

clears <WU> bit to “0”.

5. The master controller transmits data to the specified slave controller whose

SC0MOD0<WU> bit is cleared to “0”. The MSB (Bit8) <TB8> is cleared to “0”.

6. The other slave controllers (whose <WU> bits remain at 1) ignore the received

data because their MSB (Bit8 or <RB8>) are set to “0”, disabling INTRX0

interrupts. The slave controller (<WU> bit = “0”) can transmit data to the master

controller, and it is possible to indicate the end of data receiving to the master

controller by this transmission.

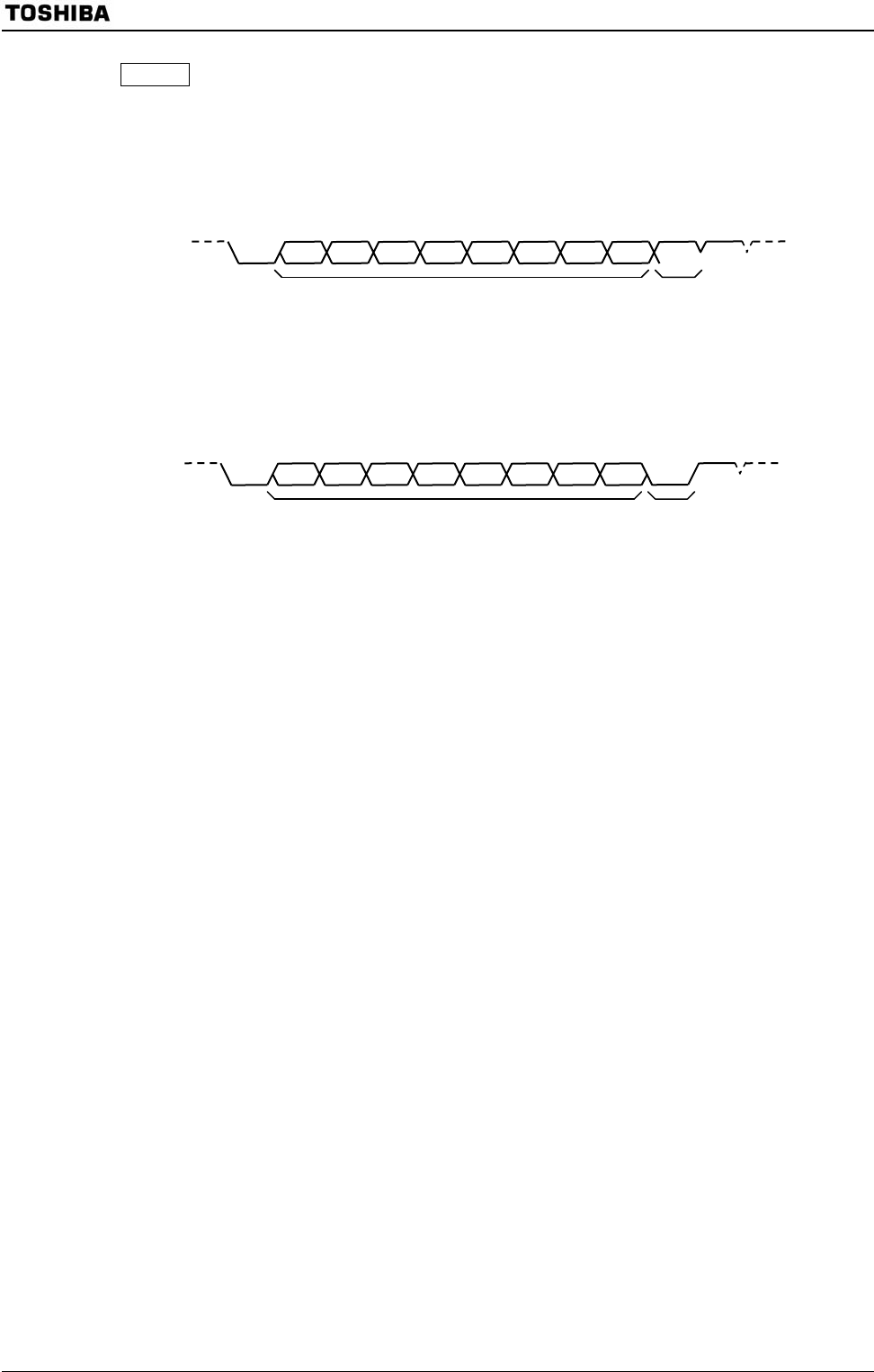

Start Bit0 123456

Select code of slave controller

7

Stop

8

“1”

Start Bit0 123456

Data

7

Stop

Bit8

“0”