TMP92CM22

2007-02-16

92CM22-241

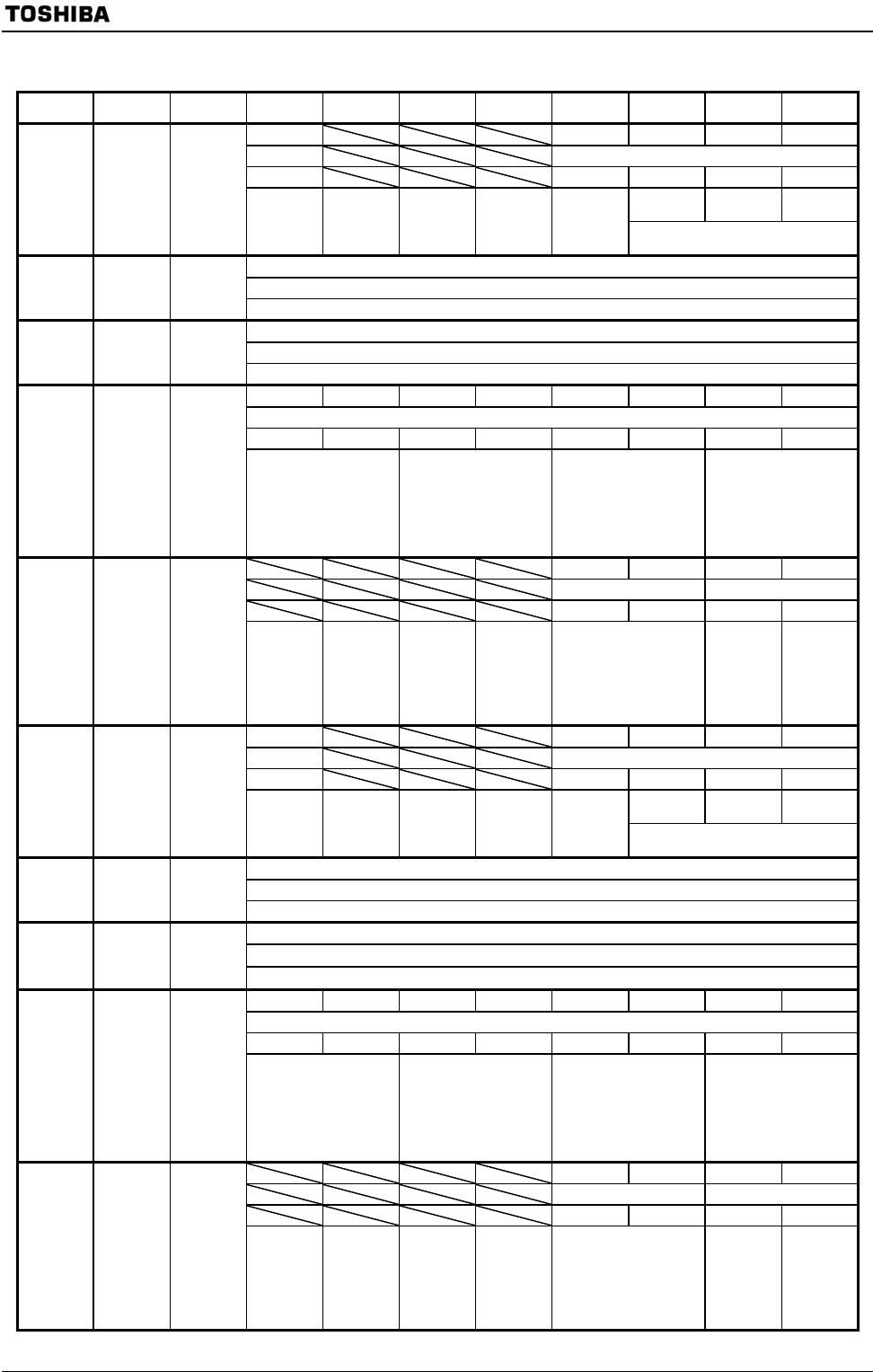

(6) 8-bit timer

Symbol Name

Address 7 6 5 4 3 2 1 0

TA0RDE I2TA01 TA01PRUN TA1RUN TA0RUN

R/W R/W

0 0 0 0 0

TMRA01

prescaler

UP counter

(UC1)

UP counter

(UC0)

TA01RUN

TMRA01

RUN

register

1100H

Double

buffer

0: Disable

1: Enable

IDLE2

0: Stop

1: Operate

0: Stop and clear

1: Run (Count up)

−

W

TA0REG

8-bit timer

register 0

1102H

(Prohibit

RMW)

Undefined

−

W

TA1REG

8-bit timer

register 1

1103H

(Prohibit

RMW)

Undefined

TA01M1 TA01M0 PWM01 PWM00 TA1CLK1 TA1CLK0 TA0CLK1 TA0CLK0

R/W

0 0 0 0 0 0 0 0

TA01MOD

TMRA01

mode

register

1104H

Operation mode

00: 8-bit timer mode

01: 16-bit timer mode

10: 8-bit PPG mode

11: 8-bit PWM mode

PWM cycle

00: Reserved

01: 2

6

10: 2

7

11: 2

8

Source clock for TMRA1

00: TA0TRG

01: φT1

10: φT16

11: φT256

Source clock for TMRA0

00: TA0IN pin

01: φT1

10: φT4

11: φT16

TA1FFC1 TA1FFC0 TA1FFIE TA1FFIS

W R/W

1 1 0 0

TA1FFCR

TMRA1

flip-flop

control

register

1105H

(Prohibit

RMW)

00: Invert TA1FF

01: Set TA1FF

10: Clear TA1FF

11: Don’t care

TA1FF

control for

inversion

0: Disable

1: Enable

TA1FF

inversion

select

0: TMRA0

1: TMRA1

TA2RDE I2TA23 TA23PRUN TA3RUN TA2RUN

R/W R/W

0 0 0 0 0

TMRA23

prescaler

UP counter

(UC3)

UP counter

(UC2)

TA23RUN

TMRA23

RUN

register

1108H

Double

buffer

0: Disable

1: Enable

IDLE2

0: Stop

1: Operate

0: Stop and clear

1: Run (Count up)

−

W

TA2REG

8-bit timer

register 2

110AH

(Prohibit

RMW)

Undefined

−

W

TA3REG

8-bit timer

register 3

110BH

(Prohibit

RMW)

Undefined

TA23M1 TA23M0 PWM21 PWM20 TA3CLK1 TA3CLK0 TA2CLK1 TA2CLK0

R/W

0 0 0 0 0 0 0 0

TA23MOD

TMRA23

mode

register

110CH

Operation mode

00: 8-bit timer mode

01: 16-bit timer mode

10: 8-bit PPG mode

11: 8-bit PWM mode

PWM cycle

00: Reserved

01: 2

6

10: 2

7

11: 2

8

Source clock for TMRA3

00: TA2TRG

01: φT1

10: φT16

11: φT256

Source clock for TMRA2

00: Reserved

01: φT1

10: φT4

11: φT16

TA3FFC1 TA3FFC0 TA3FFIE TA3FFIS

W R/W

1 1 0 0

TA3FFCR

TMRA3

flip-flop

control

register

110DH

(Prohibit

RMW)

00: Invert TA3FF

01: Set TA3FF

10: Clear TA3FF

11: Don’t care

TA3FF

control for

inversion

0: Disable

1: Enable

TA3FF

inversion

select

0: TMRA2

1: TMRA3