TMP92CM22

2007-02-16

92CM22-7

3. Operation

This section describes the basic components, functions and operation of the TMP92CM22.

3.1 CPU

The TMP92CM22 incorporates a high-performance 32-bit CPU (The TLCS-900/H1 CPU). For

a description of this CPU’s operation, please refer to the section of this data book which

describes the TLCS-900/H1 CPU.

The following sub-sections describe functions peculiar to the CPU used in the TMP92CM22;

these functions are not covered in the section devoted to the TLCS-900/H1 CPU.

3.1.1 Outline

“TLCS-900/H1 CPU” is high-speed and high-performance CPU based on

“TLCS-900/L1 CPU”. “TLCS-900/H1 CPU” has expanded 32-bit internal and external

data bus to process instructions more quickly.

Outline of “TLCS-900/H1” CPU are as follows:

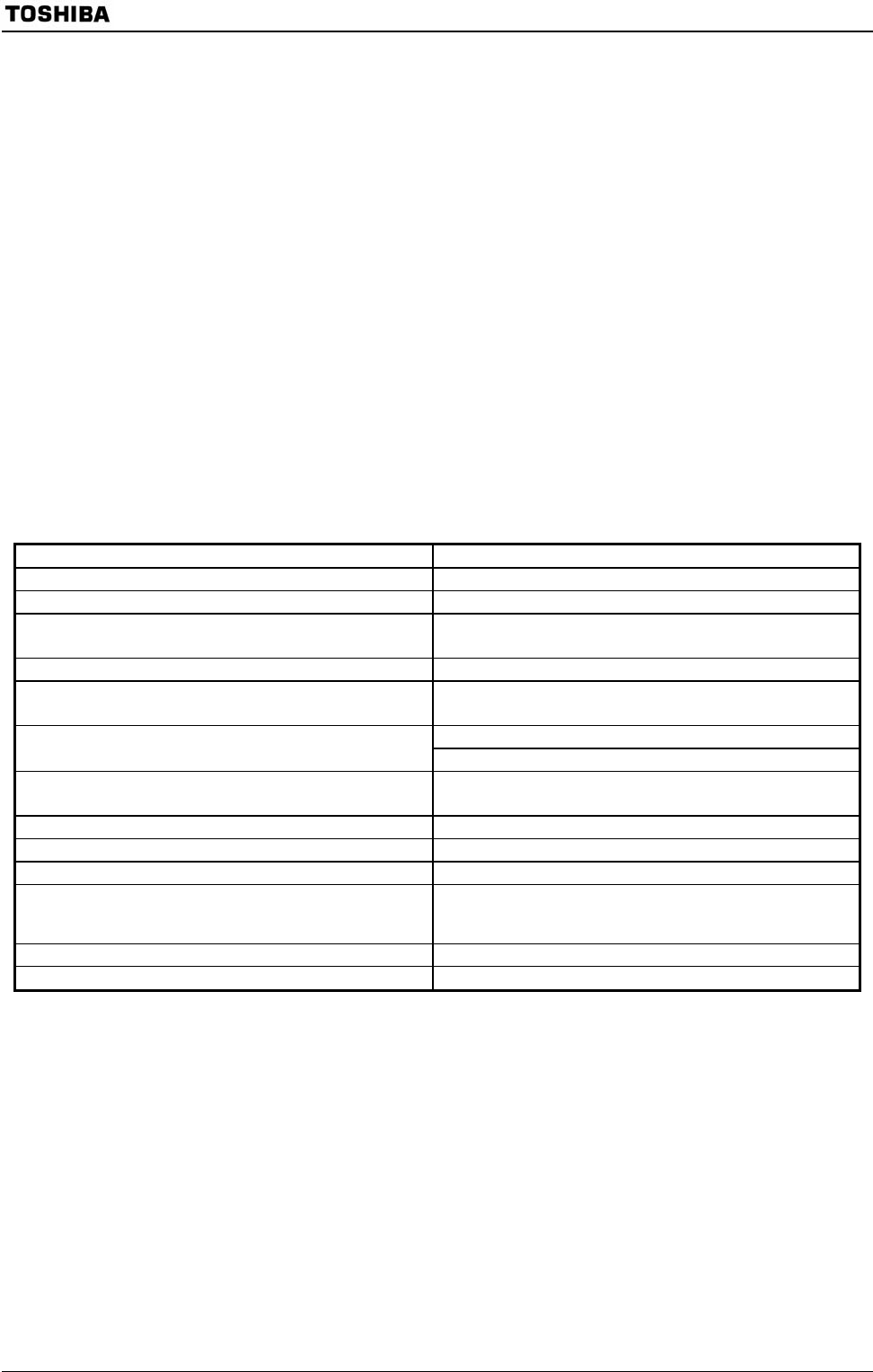

Table 3.1.1 Outline of CPU

Width of CPU address bus 24 bits

Width of CPU data bus 32 bits

Internal operating frequency 20 MHz

Minimum bus cycle 1-clock access

(50 ns at 20 MHz)

Function of data bus sizing 8 bits

Internal RAM 32 bits

1-clock access

Internal I/O 8-/16-bit 2-clock access 900/H1 I/O

8-/16-bit 5-to 6-clock access 900/H1 I/O

External device 8 bits

2-clock access (can insert some waits)

Minimum instruction execution cycle 1 clock (50 ns at 20 MHz)

Conditional jump 2 clocks (100 ns at 20 MHz)

Instruction queue buffer 12 bytes

Instruction set Compatible with TLCS-900, 900/L, 900/H, 900/L1, and 900/H2

instruction codes (However, NORMAL, MAX, MIN, and LDX

instructions is deleted)

CPU mode Only maximum mode

Micro DMA 8 channels