106 www.xilinx.com Virtex-5 FPGA ML561 User Guide

UG199 (v1.2) April 19, 2008

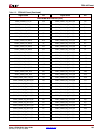

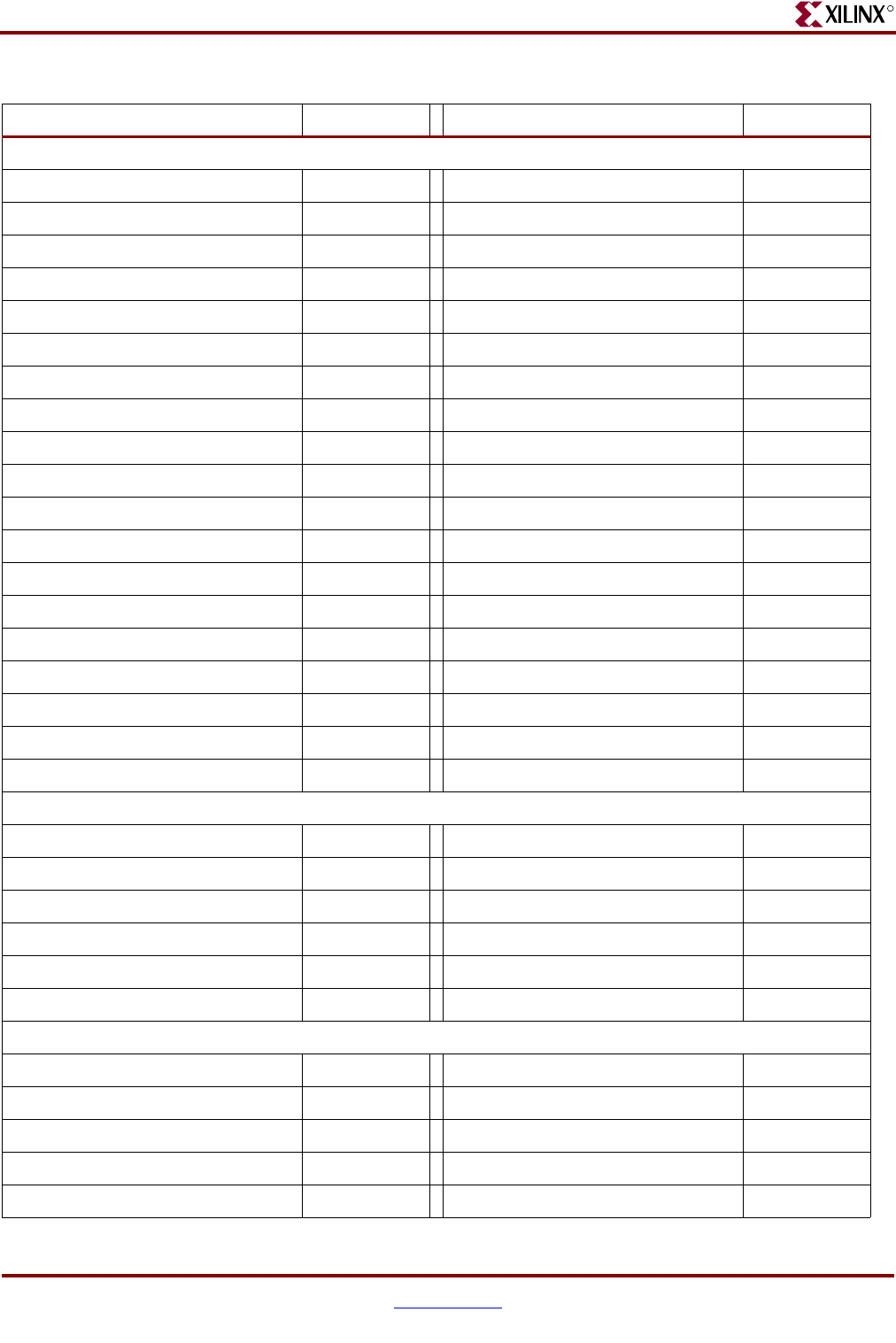

Appendix A: FPGA Pinouts

R

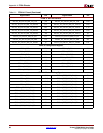

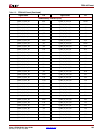

FPGA #2 Test and Debug Signals

FPGA2_DIP0 AG18 FPGA2_SOFTTOUCH_BY1_B7 H17

FPGA2_DIP1 AG15 FPGA2_SPYHOLE_BK15 P29

FPGA2_DIP2 AH15 FPGA2_SPYHOLE_BK18 W9

FPGA2_DIP3 AG20 FPGA2_TEST_HDR_BY0_B0 AE23

FPGA2_SOFTTOUCH_BY0_B0 H20 FPGA2_TEST_HDR_BY0_B1 AE22

FPGA2_SOFTTOUCH_BY0_B1 H19 FPGA2_TEST_HDR_BY0_B2 AG12

FPGA2_SOFTTOUCH_BY0_B2 H13 FPGA2_TEST_HDR_BY0_B3 AF13

FPGA2_SOFTTOUCH_BY0_B3 J14 FPGA2_TEST_HDR_BY0_B4 AG23

FPGA2_SOFTTOUCH_BY0_B4 J21 FPGA2_TEST_HDR_BY0_B5 AF23

FPGA2_SOFTTOUCH_BY0_B5 J20 FPGA2_TEST_HDR_BY0_B6 AE12

FPGA2_SOFTTOUCH_BY0_B6 H15 FPGA2_TEST_HDR_BY0_B7 AE13

FPGA2_SOFTTOUCH_BY0_B7 H14 FPGA2_TEST_HDR_BY1_B0 K12

FPGA2_SOFTTOUCH_BY1_B0 J19 FPGA2_TEST_HDR_BY1_B1 K13

FPGA2_SOFTTOUCH_BY1_B1 K18 FPGA2_TEST_HDR_BY1_B2 H23

FPGA2_SOFTTOUCH_BY1_B2 G16 FPGA2_TEST_HDR_BY1_B3 G23

FPGA2_SOFTTOUCH_BY1_B3 G15 FPGA2_TEST_HDR_BY1_B4 H12

FPGA2_SOFTTOUCH_BY1_B4 L18 FPGA2_TEST_HDR_BY1_B5 J12

FPGA2_SOFTTOUCH_BY1_B5 K17 FPGA2_TEST_HDR_BY1_B6 K22

FPGA2_SOFTTOUCH_BY1_B6 H18 FPGA2_TEST_HDR_BY1_B7 K23

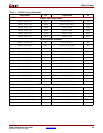

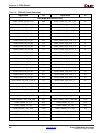

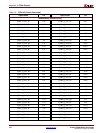

FPGA #2 Test Display Signals

FPGA2_7SEG_0_N AG17 FPGA2_7SEG_6_N AF19

FPGA2_7SEG_1_N AH18 FPGA2_7SEG_DP_N AG21

FPGA2_7SEG_2_N AE18 FPGA2_LED0 AD19

FPGA2_7SEG_3_N AF18 FPGA2_LED1 AE19

FPGA2_7SEG_4_N AG16 FPGA2_LED2 AE17

FPGA2_7SEG_5_N AH17 FPGA2_LED3 AF16

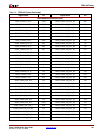

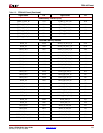

FPGA #2 External Interfaces

FPGA2_116_TX0_N G2 FPGA2_120_RX1_P D1

FPGA2_116_TX0_P F2 FPGA2_124_TX0_N B10

FPGA2_120_RX0_N A2 FPGA2_124_TX0_P B9

FPGA2_120_RX0_P A3 FPGA2_124_TX1_N B6

FPGA2_120_RX1_N C1 FPGA2_124_TX1_P B5

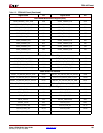

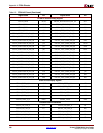

Table A-2: FPGA #2 Pinout (Continued)

Signal Name Pin Signal Name Pin