18 www.xilinx.com Virtex-5 FPGA ML561 User Guide

UG199 (v1.2) April 19, 2008

Chapter 3: Hardware Description

R

FPGA

The ML561 uses three Virtex-5 XC5VLX50T-FFG1136 devices, each in a 1136-pin,

35 mm x 35 mm BGA package. Figure 1-1, page 12 shows the memory devices associated

with the three FPGAs. Refer to Appendix A, “FPGA Pinouts,” for a complete pinout of all

Virtex-5 devices on the board. Refer to Appendix B, “Bill of Materials,” for a list of major

components on the Virtex-5 FPGA ML561 Development Board, including their reference

designators and links to their corresponding data sheets.

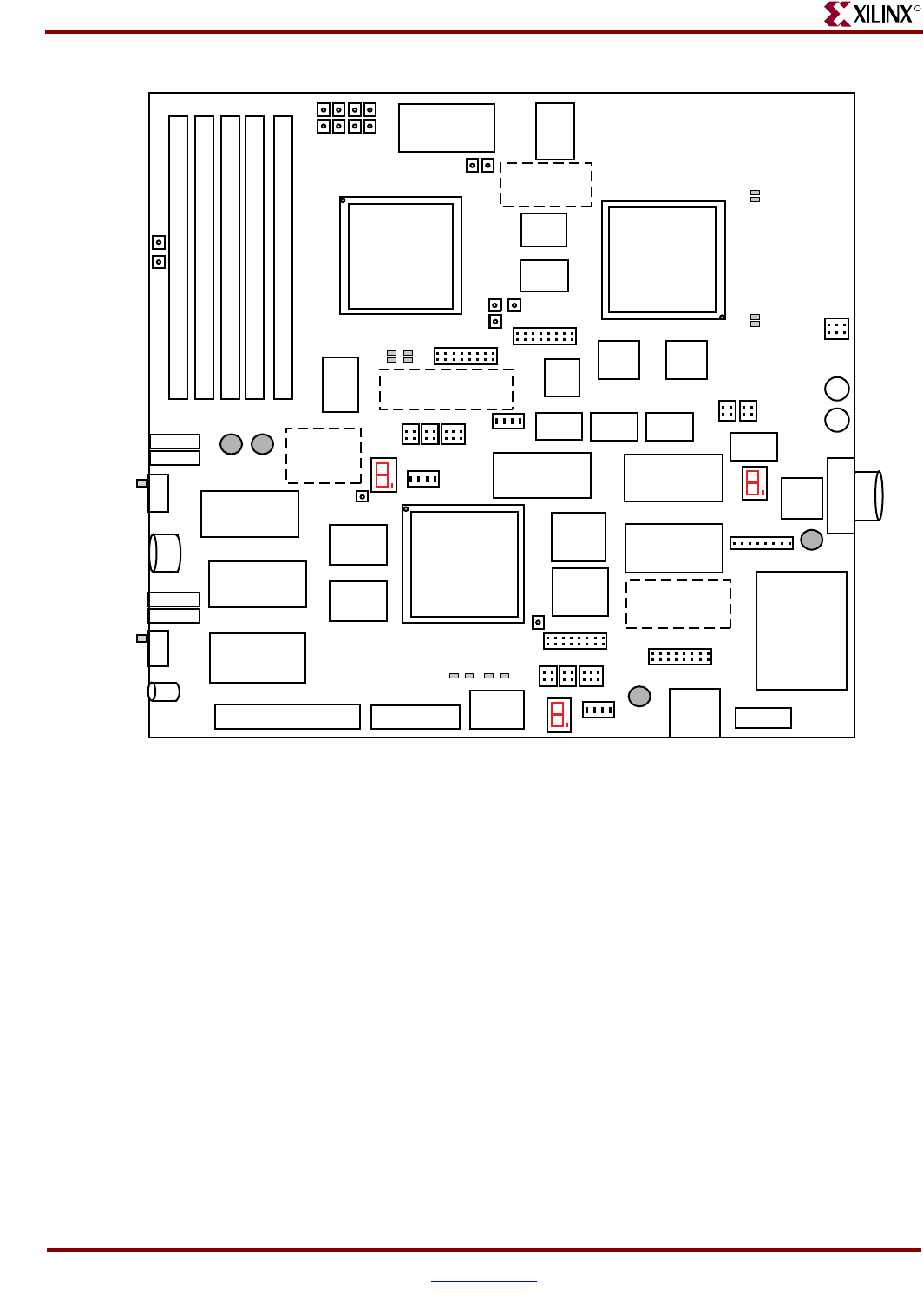

Figure 3-1: ML561 XC5VLX50T-FFG1136 Board Placement Diagram

HSTL

FPGA #3

FPGA #1

FPGA #2

SSTL18

HSTL

V

TT

& V

REF

SSTL18

V

TT

& V

REF

SSTL2

V

TT

& V

REF

V

CCAUX

/

V

CCO

V

CCINT

USB

DIP3

DIP1

DIP2

7SEG3

7SEG2

7SEG1

Config3

PROG

External

CLK

5V Input

Jack

5V Banana

Jacks

12V Banana

Jacks

12V Input

Jack

SPY

SPY

ON

OFF

OFF

ON

RESET

SPY

Config1

Config2

SPY

SSTL2

JTAG

UG199_c3_01_050106

System ACE

Controller

FPGA #3 LEDs

FPGA #1

LEDs

FPGA #1

LEDs

FPGA #2

LEDs

JTAG Test Header

Test Header 3

A1

A1

A1

Test Header 2

Test Header 1

Serial Header

HSTL

12V -> 5V

RLDRAM II

QDRII

QDRII

DDR2

AVTRX

AVC

CPLL

AVTTX

VVTTR

XC

FBD

VCC

RS-232

Driver

DDR

DDR

DDR2

MGT

CLK

MGT Connections

RLDRAM II

Clocks &

Buffers

SSTL18

_M

DIMM1

DIMM2

DIMM3

DIMM4

DIMM5

SSTL2

_M

3.3V

LCD Connector

Pwr Measure Header