38 www.xilinx.com Virtex-5 FPGA ML561 User Guide

UG199 (v1.2) April 19, 2008

Chapter 3: Hardware Description

R

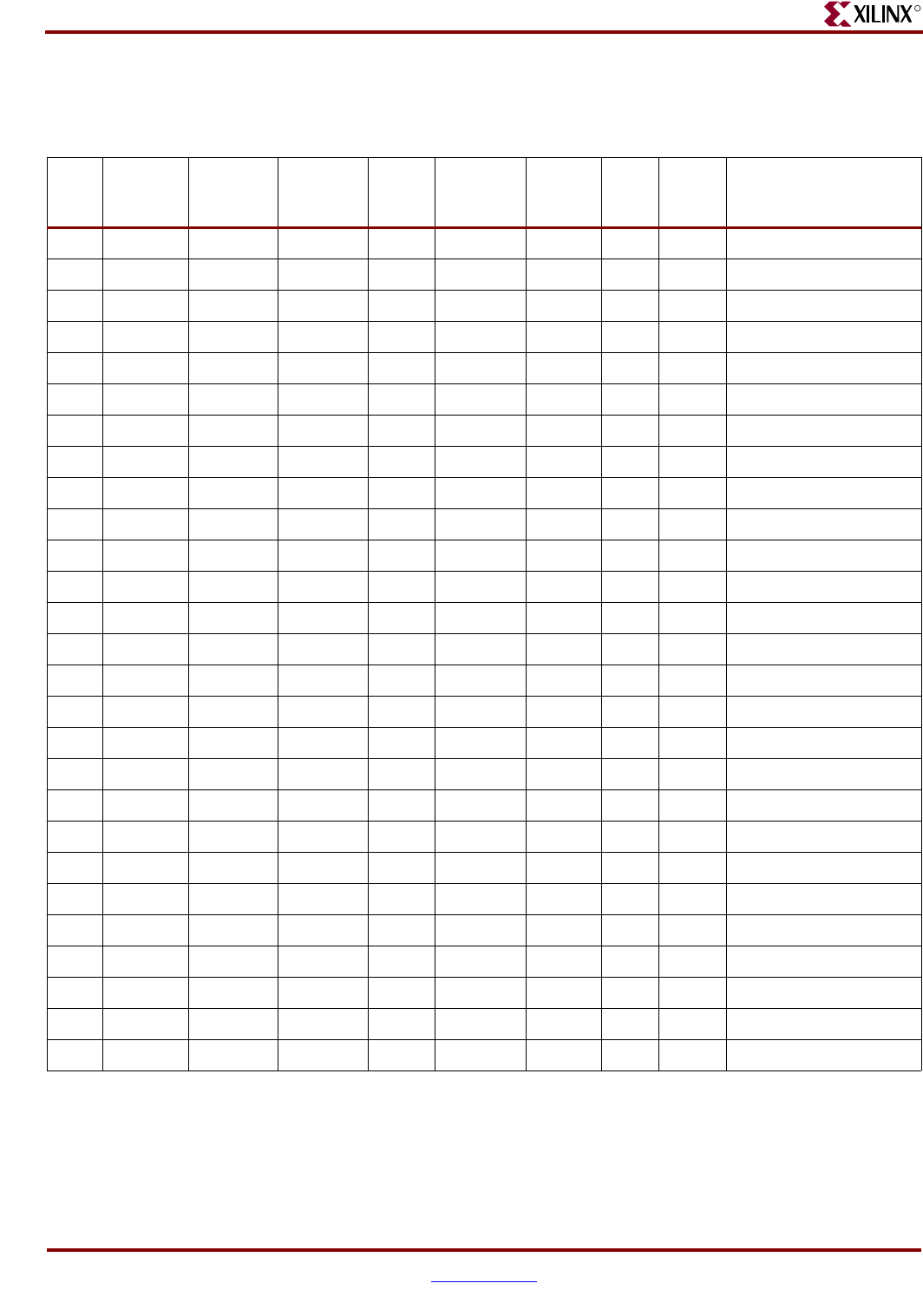

Table 3-19 shows the details of the dielectric material and construction for each layer and

the controlled impedance values for the signal layers.

Table 3-19: ML561 Revision A PCB Controlled Impedance

Seq #

Layer

Name

Type Usage

Cu

Weight

(oz.)

Substrate

Thickness

(mils)

Er

Test

Width

(mils)

Z

0

(ohms)

Comment

1 TOP Metal Signal 1.0 <Auto> 6 50 ±5 Microstrip Signal Top

2 Dielectric Substrate 3.8 4.4

3 02_GND1 Metal Plane 1.0 <Auto> Ground Plane #1

4 Dielectric Substrate 4 4.4

5 03_INR1 Metal Signal 0.5 <Auto> 4.5 50 ±5 Stripline Signal - Inner #1

6 Dielectric Substrate 5.3 4.4

7 04_PWR1 Metal Plane 1.0 <Auto> Split Power Plane #1

8 Dielectric Substrate 8 4.4

9 05_INR2 Metal Signal 0.5 <Auto> 4.5 50 ±5 Stripline Signal - Inner #2

10 Dielectric Substrate 3.2 4.4

11 06_GND2 Metal Plane 1.0 <Auto> Ground Plane #2

12 Dielectric Substrate 3 4.4

13 07_PWR2 Metal Plane 1.0 <Auto> Split Power Plane #2

14 Dielectric Substrate 3.3 4.4

15 08_PWR3 Metal Plane 1.0 <Auto> Split Power Plane #3

16 Dielectric Substrate 3 4.4

17 09_GND3 Metal Plane 1.0 <Auto> Ground Plane #3

18 Dielectric Substrate 3.2 4.4

19 10_INR5 Metal Signal 0.5 <Auto> 4.5 50 ±5 Stripline Signal - Inner #3

20 Dielectric Substrate 8 4.4

21 11_PWR4 Metal Plane 1.0 <Auto> Split Power Plane #4

22 Dielectric Substrate 5.3 4.4

23 12_INR6 Metal Signal 0.5 <Auto> 4.5 50 ±5 Stripline Signal - Inner #4

24 Dielectric Substrate 4 4.4

25 13_GND4 Metal Plane 1.0 <Auto> Ground Plane #4

26 Dielectric Substrate 3.8 4.4

27 BOTTOM Metal Signal 1.0 <Auto> 6 50 ±5 Microstrip Signal Bottom