Virtex-5 FPGA ML561 User Guide www.xilinx.com 23

UG199 (v1.2) April 19, 2008

Memory Details

R

DDR2 SDRAM DIMM

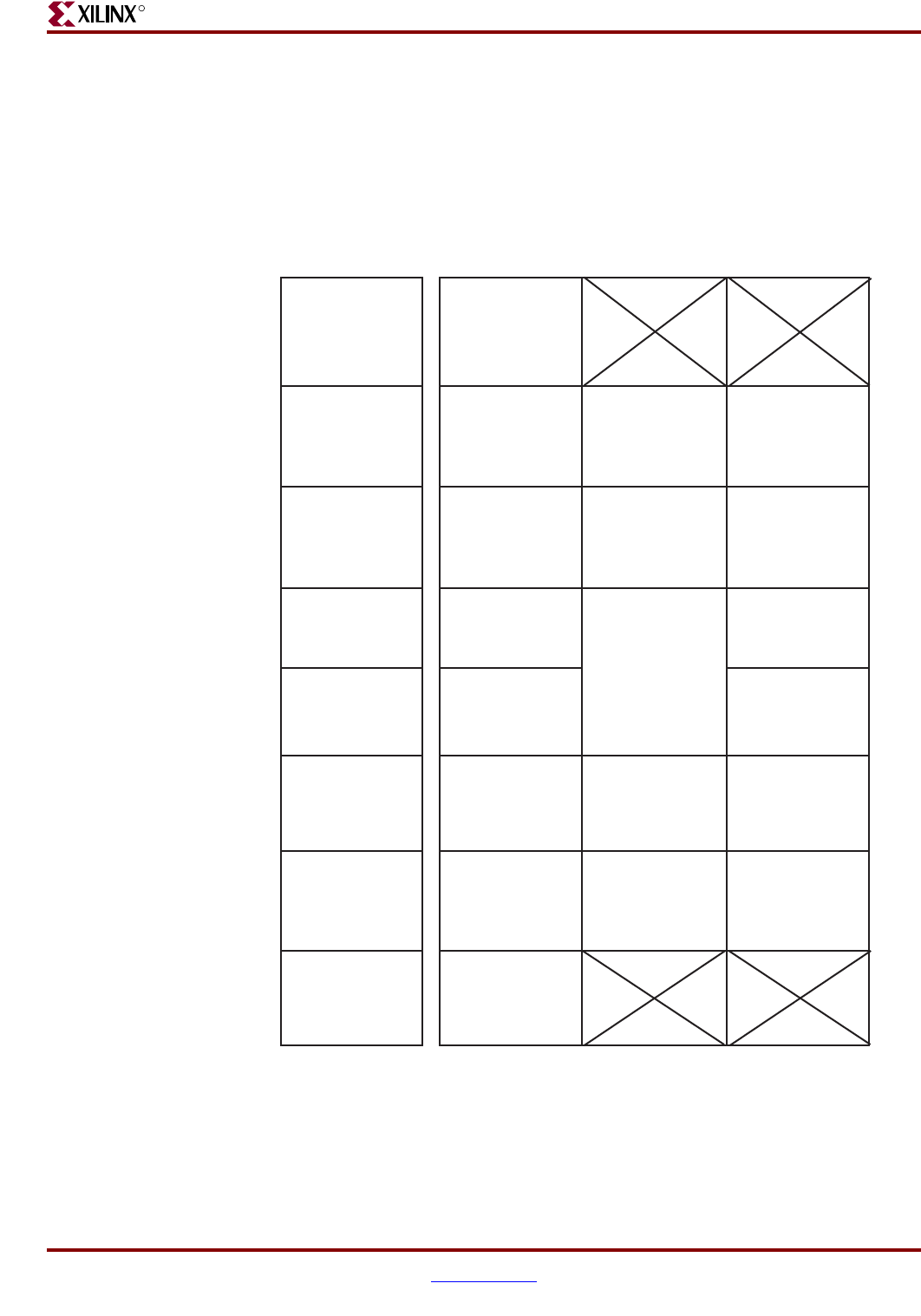

The FPGA #2 device on the Virtex-5 FPGA ML561 Development Board is connected to

DDR2 memories. The DDR2 memory interface includes a 144-bit wide DIMM connection

to up to five 240-pin DDR2 DIMM sockets.

For the 144-bit wide DIMM datapath, the data bytes are spread across multiple banks of

the FPGA #2 device. Figure 3-4 summarizes the distribution of DDR2 DIMM interface

signals among the different banks of the FPGA #2 device.

Figure 3-4: FPGA #2 Banks for DDR2 DIMM (SSTL18) Interfaces (Top View)

BANK 20 (40)

DDR2 DIMM

DQ 8, 9, 10

BANK 12 (40)

DDR2 DIMM

DQ 11, 12, CB8_15

BANK 11 (40)

DDR2 DIMM

DQ 6, 3 CB0_7

BANK 112

BANK 114

BANK 13 (40)

DDR2 DIMM

DQ 5, 7, 4

BANK 15 (40)

DDR2 DIMM

DQ 0, 1, 2

BANK 116

GTP CLK

BANK 19 (40)

DDR2 DIMM

Controls & DIMM1 Cntl

BANK 120

RX 0, 1

(Configuration)

BANK 0

BANK 3 (20)

General I/O

BANK 5 (20) BANK 23 (40)BANK 124

TX 0, 1

BANK 1 (20)

General I/O

BANK 18 (40)

DDR2 DIMM

DQ 14, 15, 13

BANK 17 (40)

DDR2 DIMM

Common Controls

BANK 118

BANK 22 (40)

DDR2 DIMM

DIMM 4 & 5 Cntl

BANK 122 BANK 21 (40)

DDR2 DIMM

DIMM 1, 2, 3 Cntl

BANK 2 (20)

Inter-FPGA MII Links

BANK 25 (40)BANK 126 BANK 6 (20)

BANK 4 (20)

Global Clock Inputs

UG199_c3_04_050106