66 www.xilinx.com Virtex-5 FPGA ML561 User Guide

UG199 (v1.2) April 19, 2008

Chapter 7: ML561 Hardware-Simulation Correlation

R

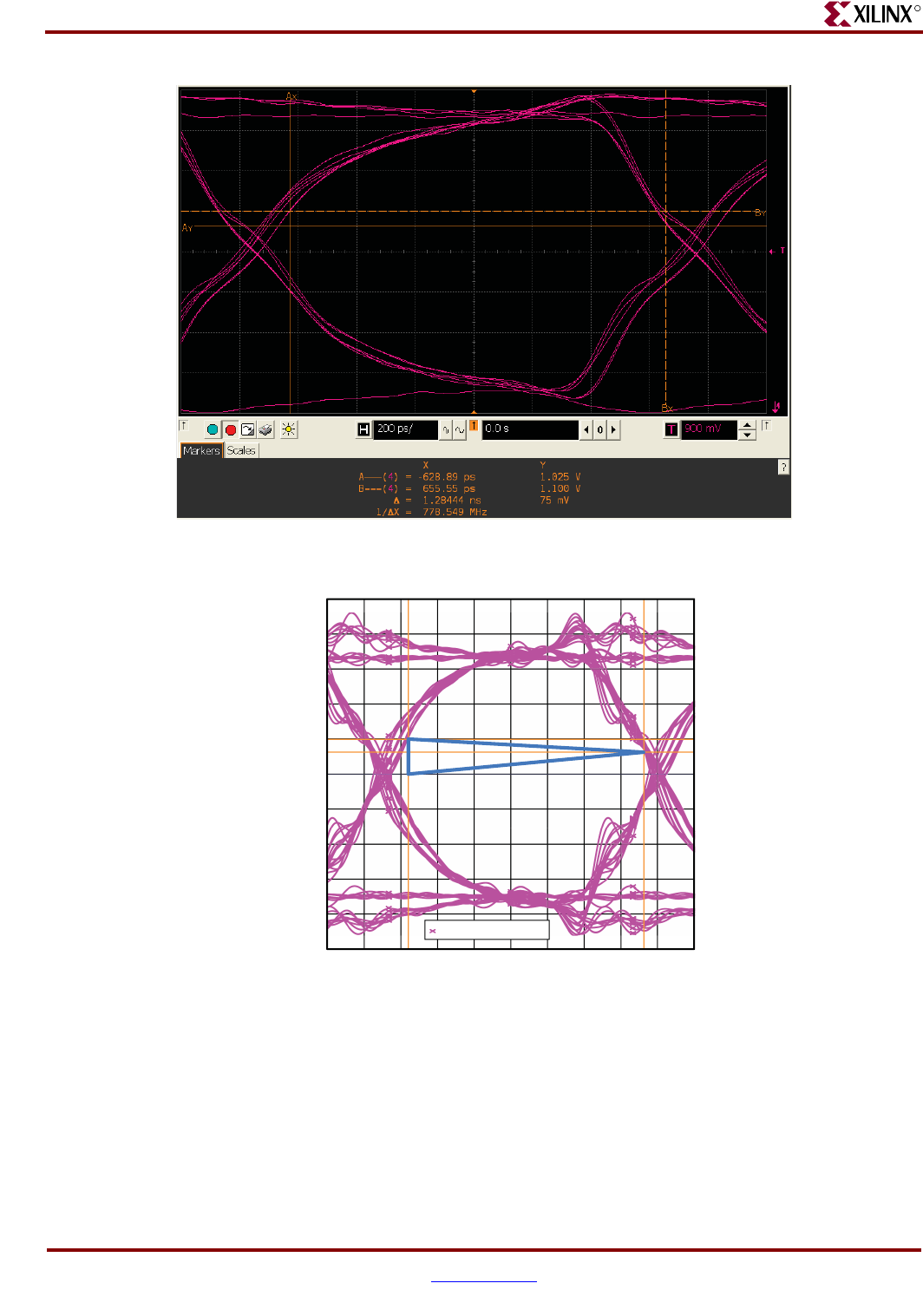

Figure 7-13: DDR2 Component Read HW Measurement - Eye Scope Shot at Probe Point (FPGA1 Via)

UG199_c7_13_071107

Figure 7-14: DDR2 Component Read Correlation - Eye Scope Shot at Probe Point (Slow Corner)

800.0 1200.0 1600.0 2000.0 2400.0 2800.0

UG199_c7_14_071107

Time (ns)

Voltage (mV)

-100.0

100.0

300.0

500.0

700.0

900.0

1100.0

1300.0

1500.0

1700.0

1900.0

Probe 3:C7.1 (at pin)

♦ 333 MHz, Slow, PRBS6, 85.9% UI

♦ Cursor 1: 697.1 mV, 1.2345 ns

♦ Cursor 2: 774.6 mV, 2.5191 ns

♦ Delta Voltage = 77.5 mV, Delta Time = 1.2846 ns (85.9% UI)