Virtex-5 FPGA ML561 User Guide www.xilinx.com 51

UG199 (v1.2) April 19, 2008

R

Chapter 6

Configuration

This chapter provides a brief description of the FPGA configuration methods used on the

Virtex-5 FPGA ML561 Development Board. This chapter contains the following sections:

• “Configuration Modes”

• “JTAG Chain”

• “JTAG Port”

• “Parallel IV Cable Port”

• “System ACE Interface”

Configuration Modes

The Virtex-5 FPGA ML561 Memory Interfaces Development Board includes several

options to configure the Virtex-5 FPGAs. The configuration modes are:

• System ACE mode

• JTAG mode

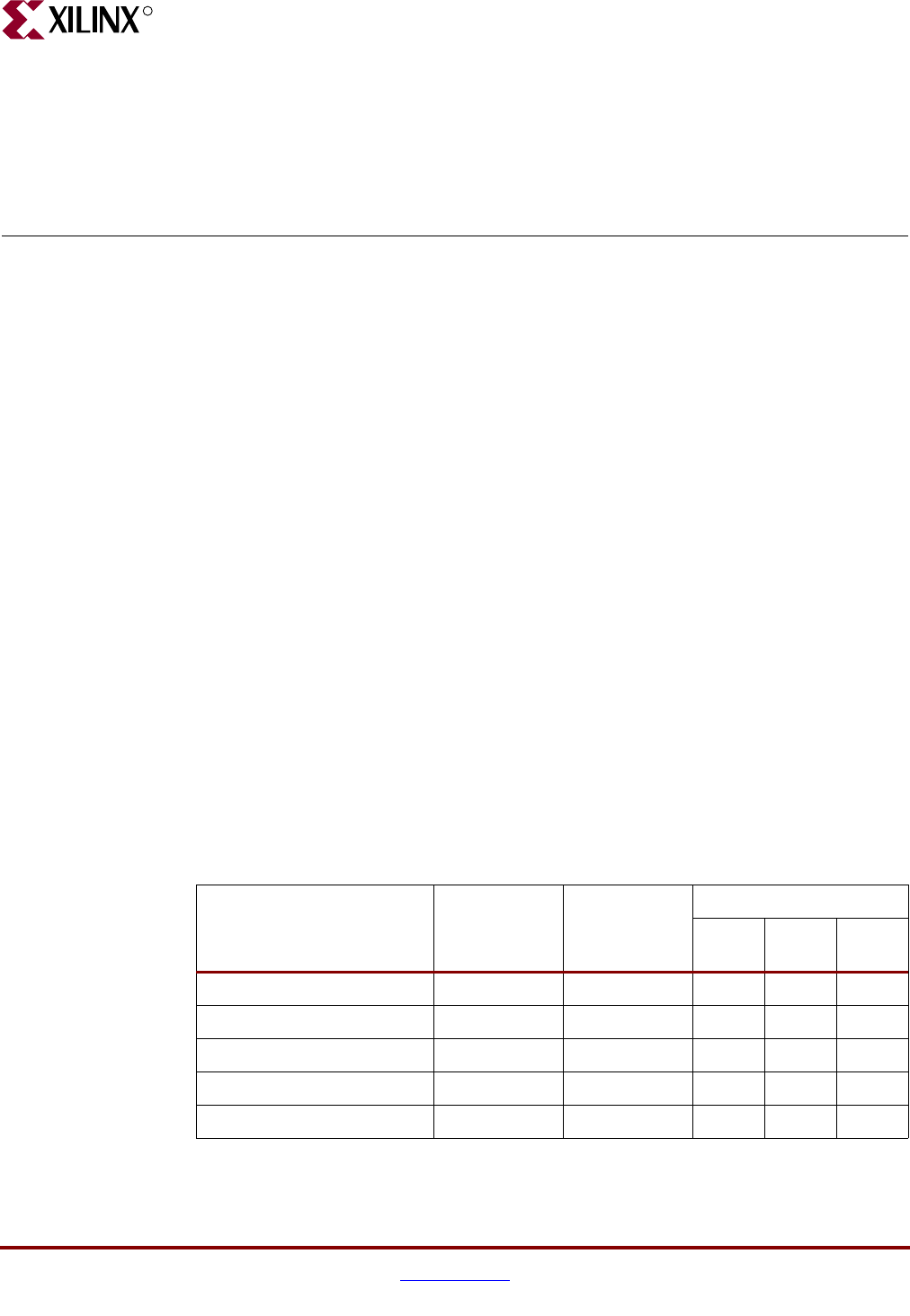

Table 6-1 shows the Virtex-5 FPGA configuration modes. The Master and Slave (Parallel)

SelectMAP configuration modes are not supported on the Virtex-5 FPGA ML561

Development Board. A separate 6-pin 3x2 header is provide for each FPGA to control the

Mode bits setting. The three headers are P27, P46, and P112 for FPGA #1, FPGA #2, and

FPGA #3, respectively. The even pins (# 2, 4, and 6) of the headers are tied to GND, and the

odd pins (# 1, 3, and 5) are connected to the respective Mode bit FPGA inputs (M0, M1, and

M2, respectively). A weak (4.7KΩ) pull-up is applied to each of these pins to set a logic '1'

by default.

Table 6-1: Configuration Modes

Mode

XCONFIG

P72

JTAG

P114

Mode Jumpers

(3,4)

5 -> 6

(M2)

3 -> 4

(M1)

1 -> 2

(M0)

Master Serial X

(1)

—

(2)

000

Slave Serial X — 1 1 1

Master SelectMAP — — 0 1 1

Slave SelectMAP — — 1 1 0

JTAG — X 1 0 1