Virtex-5 FPGA ML561 User Guide www.xilinx.com 59

UG199 (v1.2) April 19, 2008

Signal Integrity Correlation Results

R

DDR2 Component Write Operation

This subsection shows the test results for the DDR2_DQ_BY2_B3 signal from FPGA1 (U7)

to the DDR2 memory component (U12) measured at 333 MHz (667 Mb/s), where the unit

interval (UI) = 1.5 ns.

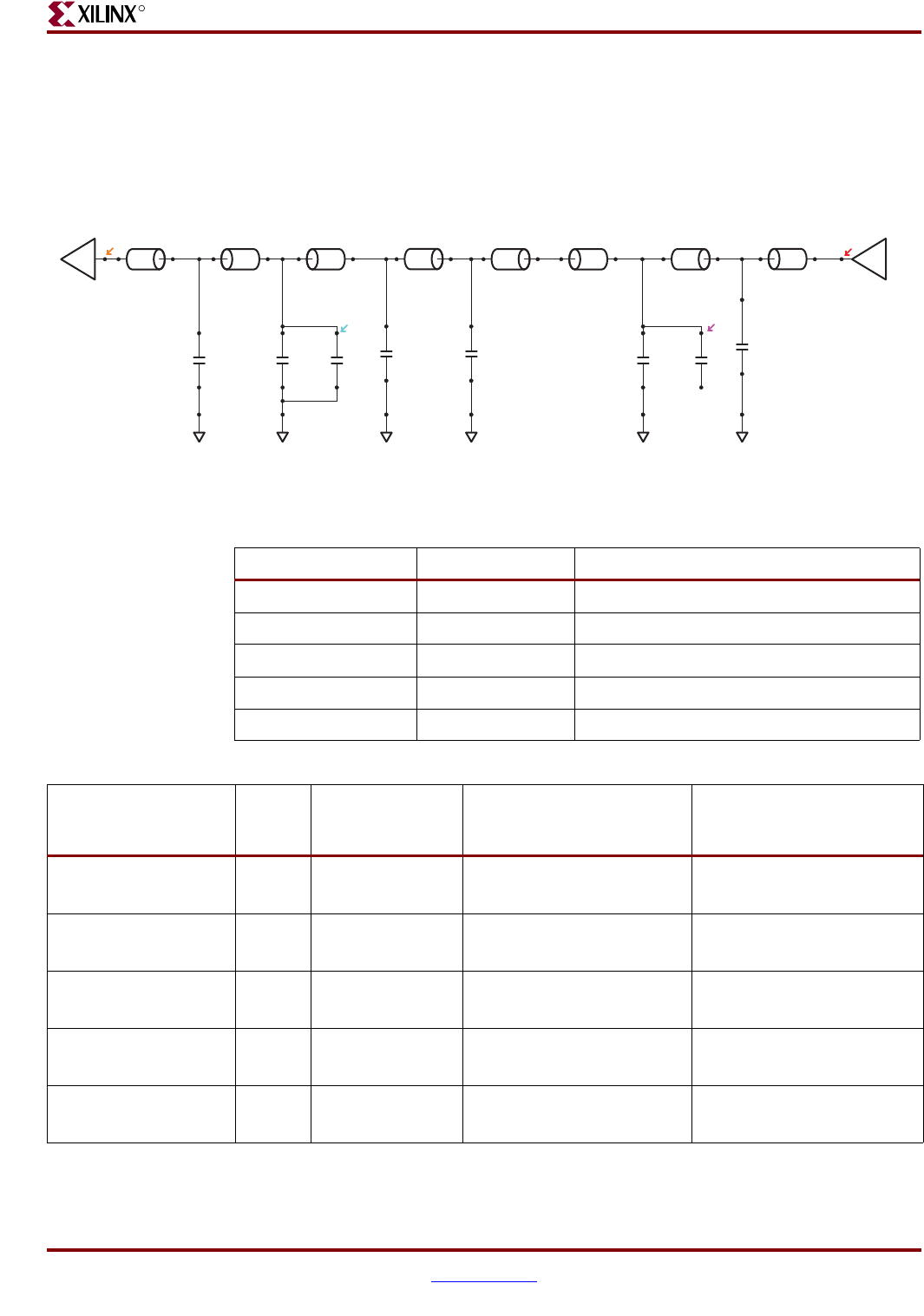

Figure 7-3: Post-Layout IBIS Schematics of DDR2 Component Write Data Bit (DDR2_DQ_BY2_B3)

UG199_c7_03_071907

MT47H32M16CC_…

DQ11

U12.D3

TL2 TL3 TL8

TL9 TL5

U7.P25

DDR2_D…

DDR2_D…

DDR2_D…

DDR2_D…

DDR2_D…

C7

C9

DDR2_D…

28.5 ohms

3.579 ps

0.022 in

DDR2_DQ_BY2_B3

71.0 ohms

27.482 ps

AutoPadstk_3

22.9 fF 22.9 fF 500.0 fF

58.1 fF 140.8 fF

365.6 fF

49.0 ohms

24.721 ps

0.164 in

DDR2_DQ_BY2_B3

58.3 ohms

25.244 ps

AutoPadstk_19

21.2 ohms

1.000 ps

AutoPadstk_3

49.1 ohms

47.132 ps

0.302 in

DDR2_DQ_BY2_B3

49.1 ohms

445.560 ps

2.852 in

DDR2_DQ_BY2_B3

28.5 ohms

4.473 ps

0.028 in

DDR2_DQ_BY2_B3

Virtex-5 FPGA

DDR2_DQ_BY2_B3

TL4 TL6

TL1

500.0 fF

22.9 fF

Table 7-1: Circuit Elements of DDR2 Component Write Data Bit

(DDR2_DQ_BY2_B3)

Element Designation Description

Driver U7.P25 FPGA SSTL18_II_DCI_O

Receiver U12.D3 DDR2 Memory, 75 Ω ODT

Probe Point C9 Via under the memory device

PCB Termination None ODT75 at load

Trace Length TL 2, 4, 9, 6, 1 3.37 inches

Table 7-2: DDR2 Component Write Operation Correlation Results

Measurement

DVW

(1)

(%UI)

ISI

(% UI)

Noise Margin

(VIH, + VIL) = Total

(% of VREF)

Overshoot / Undershoot

Margin

(% of VREF)

Hardware at probe

point

1.18 ns

(78.7%)

(80 + 80) = 160 ps

(10.7%)

(274 + 384) = 658 mV

(73.1%)

(550 + 470) = 1020 mV

(113.3%)

Simulation correlation

slow-weak corner

1.22 ns

(81.3%)

(77 + 36) = 113 ps

(7.5%)

(294 + 266) = 560 mV

(62.2%)

(461 + 490) = 951 mV

(105.7%)

Correlation Delta:

HW vs. Simulation

40 ps

(2.6%)

47 ps

(3.2%)

98 mV

(10.9%)

69 mV

(7.6%)

Extrapolation at IOB

slow-weak corner

1.27 ns

(84%)

(91 + 36) = 127 ps

(8.5%)

(300 + 270) = 570 mV

(63.3%)

(469 + 501) = 970 mV

(107.8%)

Extrapolation at IOB

fast-strong corner

1.39 ns

(92%)

(34 + 20) = 54 ps

(3.7%)

(406 + 351) = 757 mV

(84.1%)

(304 + 381) = 685 mV

(76.1%)

Notes:

1. DVW = Data Valid Window, ISI = Inter-Symbol Interference