Virtex-5 FPGA ML561 User Guide www.xilinx.com 127

UG199 (v1.2) April 19, 2008

Hardware Schematic Diagram

R

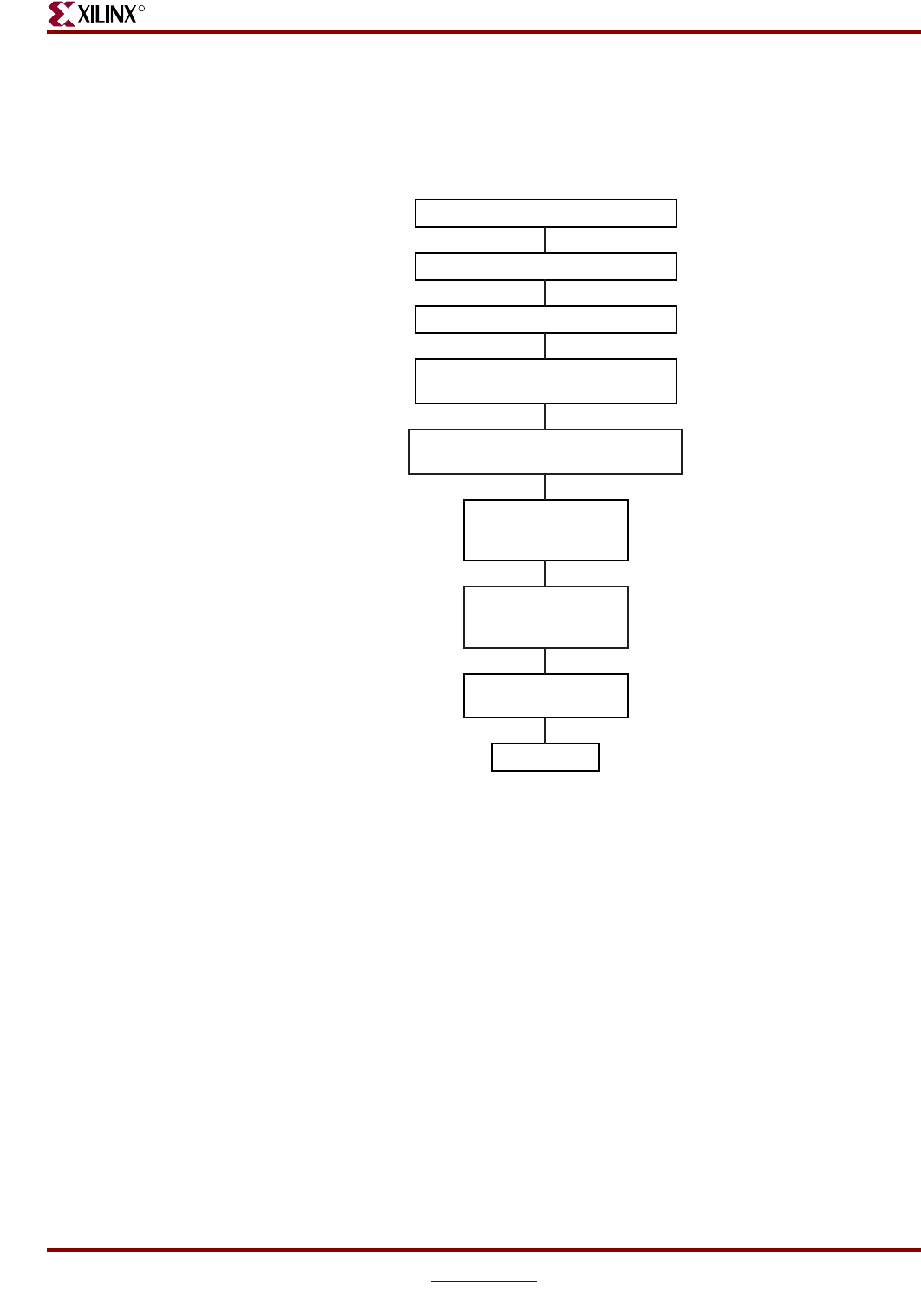

The voltage and contrast settings must be configured before the LCD panel is ready for

operation. Figure C-6 shows the initialization procedure required to set up the LCD

controller.

Operation Example of the 64128EFCBC-3LP

The KS0713 LCD controller has several default settings of operation on the LCD panel

PCB. Some settings are forced through direct bonding on the chip. The default settings are:

• Master mode

• Parallel mode

• Internal oscillator

• Duty cycle ratio is set to 1/65

• Voltage converter input is between 2.4V ≤ VDD ≤ 3.6V, where VDD connects to 3.3V

• Internal voltage divider resistors

• Temperature coefficient is set to -0.05%/° C

• Normal power mode is set

Figure C-6: LCD Controller Initialization Flow

End Initialization

Regulator Resistor Select

Set Reference Voltage

FPGA Configured and Application Running

RESETB Pin is Taken HIGH

Start FPGA Configuration

RESETB Pin is Kept LOW

RESETB Pin is Kept LOW

Setup Instruction Flow

Wait longer than 1 ms between

each instruction to let the voltages stabilize.

The on-chip resistors are used.

Therefore, the selection MUS

T be

set to 101.

Setting Reference Voltage

is a two-pass instruction:

- Set Reference Voltage Mode

- Set Reference Voltage Register

LCD Bias

DUTY0, 1 is "11".

LCD Bias 0 = 1/7

LCD Bias 1 = 1/9

SHL Select

- SHL = 0 COM1 --> COM64

- SHL = 1 COM64 --> COM1

ADC Select

- ADC = 0 SEG1 --> SEG132

- ADC = 1 SEG132 --> SEG1

Board Power Supply Start

Power ON

Voltage Converter ON

Voltage Regulator ON

Voltage Follower ON

ADC Select

SHL Select

LCD Bias Select

UG199_C_06_050106