4-8 Theory of Operation

4.3.4 ALI M1523 (PCI, Cache and Memory Controller)

The M1523 is a bridge between PCI and ISA bus, providing full PCI and ISA compatible functions.

The M1523 has Integrated System Peripherals (ISP) on-chip and provides advanced features in the

DMA controller. This chip contains the keyboard controller, real-time clock and IDE master

controller. This chip also supports the Advanced Programmable Interrupt controller (APIC)

interface.

One eight-byte bidirectional line buffer is provided for ISA/DMA master memory read/writes. One

32-bit wide posted-write buffer is provided for PCI memory write cycles to the ISA bus. It also

supports a PCI to ISA IRQ routing table and level-to-edge trigger transfer.

The chip has two extra IRQ lines and one programmable chip select for motherboard Plug and Play

functions. The interrupt lines can be routed to any of the available ISA interrupts.

The on-chip IDE controller supports two IDE connectors for up to four IDE devices providing an

interface for IDE hard disk and CD-ROMs. The ATA bus pins are dedicated to improve the

performance of IDE master.

The M1523 supports the Super Green feature for Intel and Intel compatible CPUs. It implements

programmable hardware events, software event and external switches (for suspend/turbo/ring-in).

The M1523 provides CPU clock control (STPCLKJ). The STPCLKJ can be active (low) or inactive

(high) in turn by throttling control.

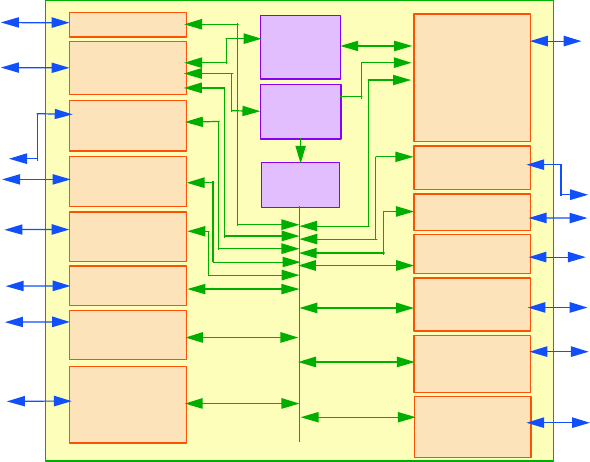

A simplified block diagram of the M1523 chip is shown in Figure 4-3 and the associated pinouts are

provided in Figure 4-4.

M1523 Block Diagram

DATA

Buffer

Control

Address

Buffer

Decoder

Clock & Reset

PCI BUS

Interface

UNIT

PCI

Arbiter

Interface

ISA

Interrupt

UNIT

PCI

Interrupt

UNIT

CPU

Interface

USB

Interface

(reserved)

PCI

IDE

Master

Interface

ISA BUS

Interface

UNIT

DMA

Refresh

UNIT

PMU or APIC

Interface

PS2/AT

Keyboard

Controller

Timer

UNIT

MISC.

Logic

REAL

Time

Clock

PWG

CPURST

RSTDRV

OSC14M

PCICLK

CBEJ[3:0]

AD[31:0]

FRAMEJ

TRDYJ

IRDYJ

STOPJ

DEVSELJ

SERRJ

PAR

PHOLDJ

PHLDAJ

FERRJ

IRQ[15:14]

IRQ[11:3]

INTAJ/M1II

NTBJ/S0

INTCJ/S1

INTDJ/S2

IGNNEJ

INTR

NMI

A20MJ

USBCLK

USBP[11:10]

IDRQ[0:1]

IDAKJ[0:1]

IDERDY

IDEIORJ

IDEIOWJ

IDESCS3J

IDESCS1J

IDEPCS3J

IDEPCS1J

IDE_A[2:0]

IDE_D[15:0]

SD[15:8]

XD[7:0]

SA[19:0]

SBHEJ

LA[23:17]

IO16J

M16J

MEMRJ

MEMWJ

AEN

IOCHRDYJ

NOWSJ

IOCHKJ

SYSCLK

BALE

IORJ

IOWJ

SMEMRJ/LMEGJ

SMEMWJ/RTCAS

EXTSW

STPCLKJ

SPKR

SIRQI

XDIR

SPLED

ROMCSJ

SIRQII

RTC32KI

RTC32KII

KBINH/IRQ1

KBCLK/KBCSJ

KBDATA

MSCLK

IRQ12/MDATA

DREQ[7:5]

DREQ[3:0]

DACKJ[7:5]

DACK2J/3J

TC

REFSHJ

Figure 4-3 M1523 Chip Simplified Block Diagram