Chapter 4 System Support

P dress Register

I/O Port 0CF8h, R/W, (32-bit access only)

PCI Configuration Data Register

I/O Port 0CFCh, R/W, (8-, 16-, 32-bit access)

PCI BUS TRANSACTIONS

The PCI bus consists of a 32-bit path (AD31-00 lines) that uses a multiplexed scheme for

handling both address and data transfers. A bus transaction consists of an address cycle and one

or more data cycles, with each cycle requiring a clock (PCICLK) cycle. High performance is

realized during burst modes in which a transaction with contiguous memory locations requires

CI Configuration Ad

evices on the PC ply wi PCI protoc at allows figurati of that dev

oftware. In th io echani h Bus

tio f a PCI . Th

ddress reg S 8h alue that specifies the PCI bus, PCI

cc e c tion data r ( _D

CFCh contain

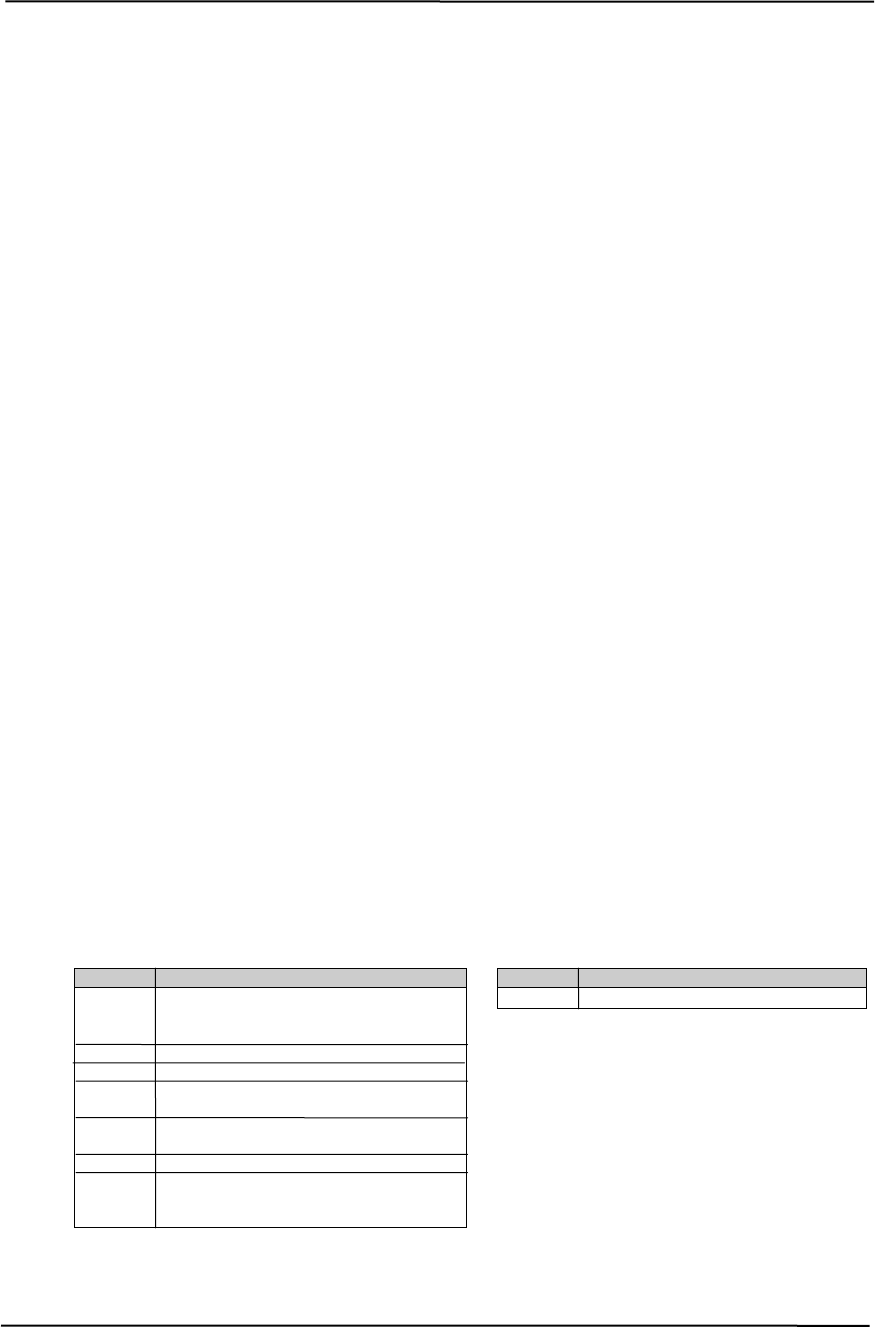

Bit

Function it Fun

31 Configuration En

0 = Disabled

1 = Enable

30..24 Reserved - rea

23..16 Bus Number. S I bus

15..11 PCI Device Nu ects PC

device for acc

4.2.1

at only one address cycle be conducted and subsequent data cycles are completed using auto-

cremented addressi

onf p bus).

4.2.1.1 I/O and Memory Cycles

For I/O ecode (AD31..0) for byte-level addressing

is handled by the appropriate PCI device. For memory addressing, PCI devices decode the

essing and check the AD1,0 lines for burst (linear-

incrementing) mode. In burst mode, subsequent data phases are conducted a dword at a time with

4.2.1.2 Configuration Cycles

D I bus must com th ol th con on ice by

s is system, configurat n m sm #1 (as described in t e PCI Local

specification Rev. 2.1) is employed. This method uses two 32-bit registers for initiating a

configuration cycle for accessing the configura n space o device e configuration

a ister (CONFIG_ADDRE S) at 0CF holds a v

device, and specific register to be a essed. Th onfigura registe CONFIG ATA) at

0 s the configuration data.

B ction

able

31..0 Configuration Data.

d/write 0s

elects PC

mber. Sel I

ess

Function Number. Selects function of

e.

7..2

1,0

01 = Type 1

th

in n Four types of d ss n

ecial. A odin but p to vic e I

g. ad re cycl

g is distri

es ca take pl

ed (left u

ace on the P

each de

CI bus; I/

e on th

O, memory,

c iguration, and s ddress dec PC

and memory cycles, a standard 32-bit address d

AD31..2 lines for dword-level addr

addressing assumed to increment accordingly (four bytes at a time).

10..8

selected PCI devic

Register Index. Specifies config. reg.

Configuration Cycle Type ID.

00 = Type 0

Compaq Evo and Workstation Personal Computers

Featuring the Intel Pentium 4 Processor

Second Edition – January 2003

4-4