Technical Reference Guide

RATION

at

NT), and FRAME signals are used

by PCI bus masters for gaining access to the PCI bus. When a PCI device needs access to the PCI

bus (and does not already own it), the PCI device asserts it’s REQn signal to the PCI bus arbiter (a

ler component). If the bus is available, the arbiter asserts the GNTn

signal to the requesting device, which then asserts FRAME and conducts the address phase of the

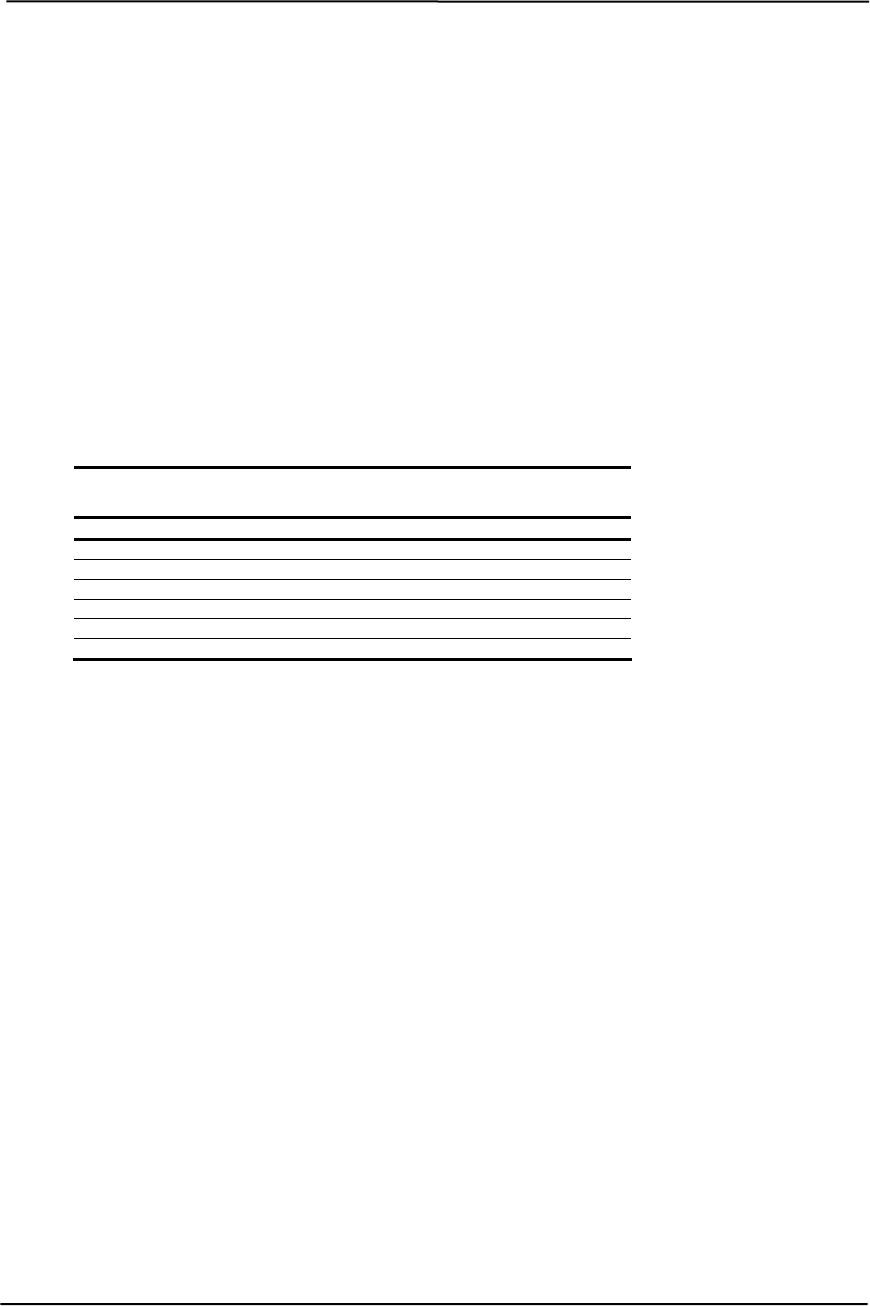

e 4-3. PCI Bus Mastering Devices

Table 4-3.

4.2.2 PCI BUS MASTER ARBIT

The PCI bus supports a bus master/target arbitration scheme. A bus master is a device that has

been granted control of the bus for the purpose of initiating a transaction. A target is a device th

is the recipient of a transaction. The Request (REQ), Grant (G

function of the system control

transaction with a target. If the PCI device already owns the bus, a request is not needed and the

device can simply assert FRAME and conduct the transaction. Table 4-3 shows the grant and

request signals assignments for the devices on the PCI bus.

Tabl

PCI Bus Mastering Devices

REQ/GNT Line Device

REQ0/GNT0 PCI Connector Slot 1

REQ1/GNT1 PCI Connector Slot 2

REQ2/GNT2 PCI Connector Slot 3 [1]

REQ3/GNT3 PCI Connector Slot 4 [2]

REQ4/GNT4 PCI Connector Slot 5 [2]

GREQ/GGNT AGP Slot

NOTE:

urable Minitower models only.

wer models only

m

ecified by the PCI specification. The bus parking policy allows for the current PCI bus owner

idge) to maintain ownership of the bus as long as no request is asserted

a t most CPU-to-DRAM and AGP-to-DRAM accesses can occur

oncurrently with PCI traffic, therefore reducing the need for the Host/PCI bridge to compete for

[1] Desktop and Config

[2] Configurable minito

CI bus arbitration is based on a round-robin scheme that complies with the fairness algorithP

sp

(excepting the PCI/ISA br

by nother agent. Note tha

c

PCI bus ownership.

Compaq Evo and Workstation Personal Computers

Featuring the Intel Pentium 4 Processor

Second Edition - January 2003

4-7