Chapter 4 System Support

4.4

s

ded on a priority

4.4.1 I U

The microprocessor uses tw ware interrupts; maskable and nonmaskable. A

m kable interr be e disabled within the microprocessor by the use of the STI and

C instructions. A nonma annot be masked off within the microprocessor,

a ugh it may ibited or software means external to the microprocessor.

4.4.1.1 askab erru

The maskable i t is a l used by peripheral functions within the

s to get th ion o eripheral functions produce a unique INTA-H

( Q0-15 (ISA) sig asserts the interrupt

e microprocessor. The microprocessor halts execution to determine the source

of the in vices the peripheral as appropriate.

the routing of PCI and ISA interrupts. Most IRQs are routed through the I/O

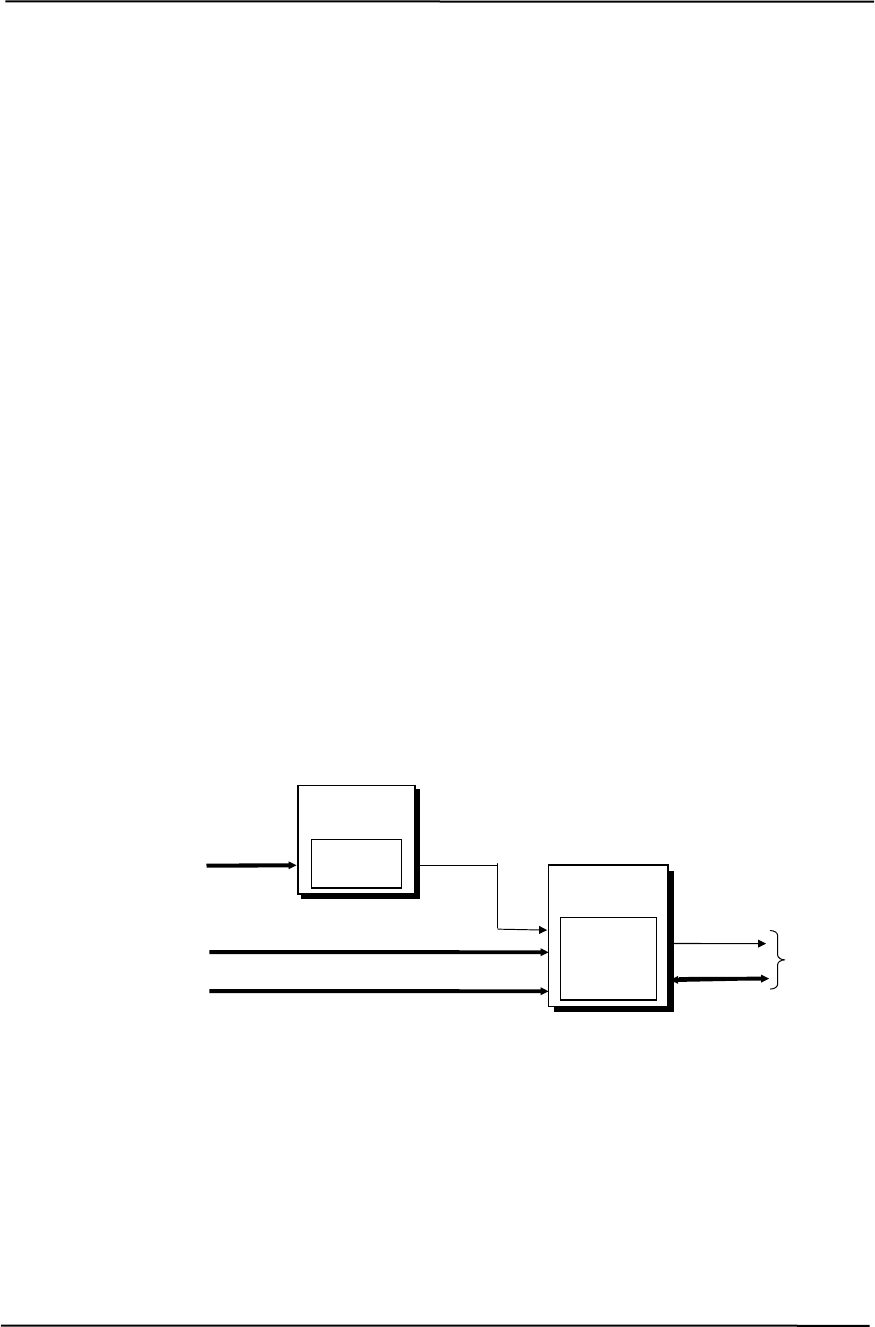

Figure 4-9. M ble In Processing, Block D gram

Interrupts may be roce o o ( bl gh th 10 Se uti

♦ 825

♦ API

SYSTEM RESOURCES

This section describes the availability and basic control of major subsystems, otherwise known a

resource allocation or simply “system resources.” System resources are provi

nts. basis through hardware interrupts and DMA requests and gra

NTERR PTS

o types of hard

as upt can nabled or

LI skable interrupt c

ltho be inh by hardware

M le Int pts

nterrup hardware-generated signa

ystem e attent f the microprocessor. P

PCI) or IR nal that is routed to interrupt processing logic that

(INTR-) input to th

terrupt and then ser

igure 4-9 showsF

controller, which contains a serializing function. A serialized interrupt stream is applied to the

82801 ICH2.

IRQ3..7,

I/O Cntlr.

9..12,

14,15

Interrup

aska terrupt ia

p sse ind ne tw of m esod sel taec e th our e F tup lity):

INTA-..H-

9 mode

C mode

82801

ICH2

Interrupt

IRQ14,15

IDE

Hard Drives

INTR-

Processing

Serial IRQ

I/O &

SM Functions

Serializer

Processor

PCI Peripherals

LPC47B367

t

APIC bus

Compaq Evo and Workstation Personal Computers

Featuring the Intel Pentium 4 Processor

Second Edition – January 2003

4-16