Chapter 4 System Support

Figure 4-7. AGP 4X Data Transfer (Peak Transfer Rate: 1064 MB/s)

4.3.2 AGP CONFIGURATION

qu the configuration of certain parameters involvin em memory

c adapter. The AGP bus interface is configured as a PCI device

s, from the

I

NOTE: Configuration of the AGP bus interface involves functions 0 and 1 of the

AGP bus operations re

ccess by the AGP grap

ire

s

g syst

a hi

integrated within the nort

CI bus perspective, tr

onfiguration registers

h bridge (MCH, device 1) component. The AGP function i

eated essentially as a PCI/PCI bridge and configured through PC

(Table 4-6). Configuration is accomplished by BIOS during POST.

P

c

MCH. Function 0 registers (listed in Table 3-4) include functions that affect basic

control (GART) of the AGP.

ion 1)

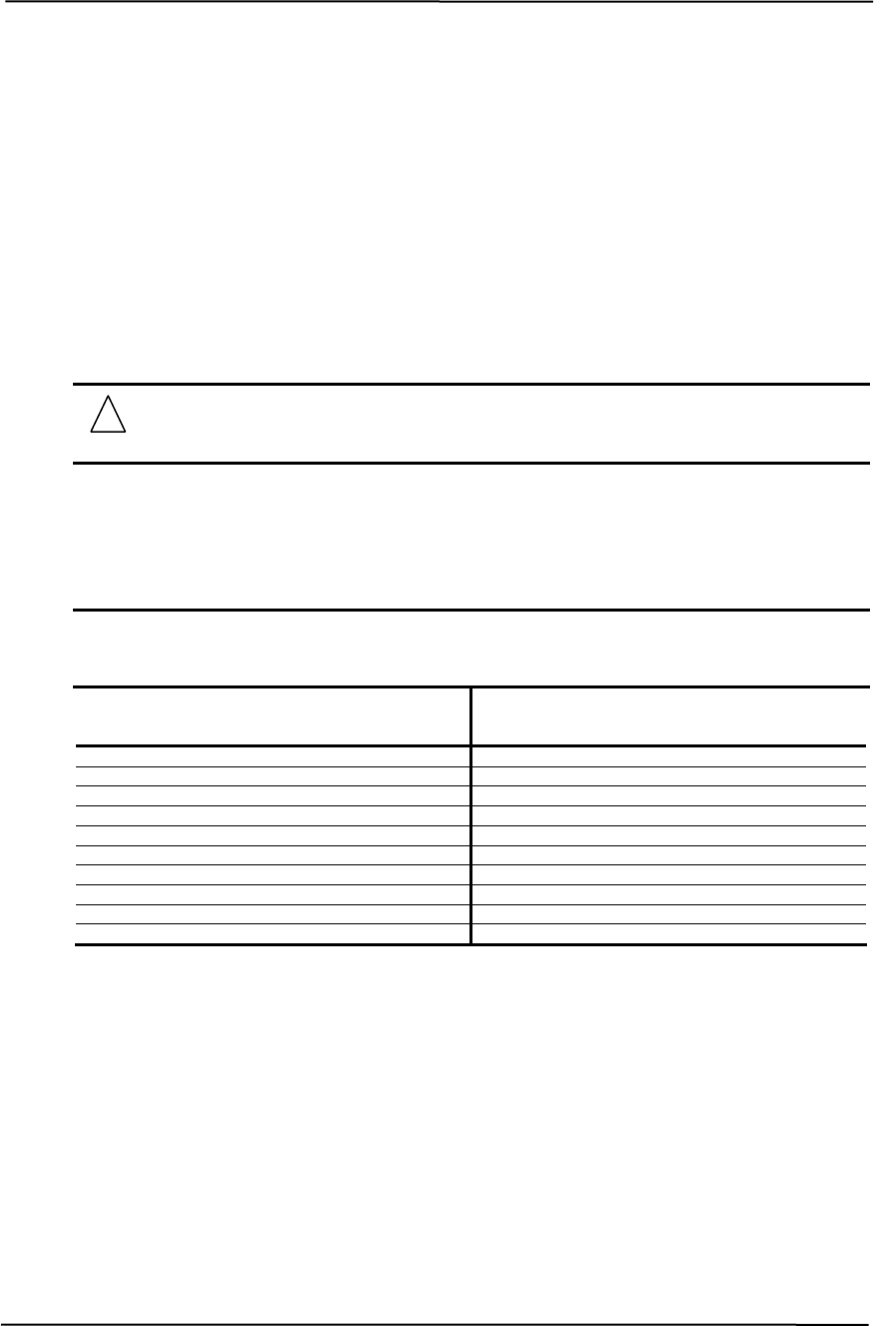

Table 4-6. PCI/AGP Bridge Configuration Registers (MCH, Funct

Table 4-6.

PCI/AGP ge n C tion gi

, Fun

Brid Functio onfigura Re sters

(MCH ction 1)

PCI

fig

r.

Regis

P

C

A

R ste

Reset

Value

Con .

Add

ter

Reset

Value

CI

onfig.

ddr.

egi r

00, 01h Vend h 1 Sec. Master Latency T 00h or ID 8086 Bh imer

02, 03h evic 1 I/O Base Address F0h D e ID 1131h Ch

04, 05h Comm 1 I/O Limit Address 00h and 0000h Dh

06, 07h Statu h 1E, 1Fh Sec. PCI/PCI Status s 0020 02A0h

08h Revision ID 2 Memory dress00h 0, 21h Base Ad FFF0h

0A, 0B Class Code 2 Memory ddress 0000h h 0406h 2, 23h Limit A

0Eh Head 2 P tch se Aer Type 01h 4, 25h refe Mem. Ba ddr. FFF0h

18h Prima Numbe 2 P tch mit Ary Bus r 00h 6, 27h refe Mem. Li ddr. 0000h

19h Secon Bus Number 3 P CI ontro 00h dary 00h Eh CI/P Bridge C l

1Ah Subordinate Bus Number 3F-FFh R rve h 00h ese d 00

Assum arked l s/ga as reser Refer to cum tation fo ed

register d riptions.

dapter (act ally resident troller) is c figu d as a st rd PCI

NOTE:

e unm ocation ps ved. Intel do en r detail

esc

The AGP graphics a u its con on re anda device.

Compaq Evo and Workstation Personal Computers

Featuring the Intel Pentium 4 Processor

Second Edition – January 2003

4-14