PMC/PCI INTERFACE

Bridge EEPROM

3-6 CC1000dm User’s Manual 10004281-02

3

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

BRIDGE EEPROM

The PLX PCI 6254 PCI-to-PCI bridge utilizes ROM interface signals to initialize the PCI

6254 registers. The following table briefly describes these signals (see the data book for

complete information):

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

PCI 6254 CONFIGURATION REGISTERS

The PCI 6254 can be configured to act as either a transparent or non-transparent PCI-

to-PCI bridge by selecting the appropriate jumper on JP5 (see page 2-9). In transparent

mode, the CC1000dm system PCI bus is connected to the PCI 6254 primary port. The

PCI 6254 non-transparent mode acts as a memory-mapped PCI device with the primary

port connected to the cPCI backplane.

Signal Description:

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

EEPCLK The EEPROM Clock output signal to the EEPROM interface is used during

autoload and for VPD functions. This pin is tri-stated if EE_EN* = 1.

EEPDATA The EEPROM Serial Data interfaces to the EEPROM (bi-directional). This pin

is tri-stated if EE_EN* = 1.

EE_EN* The EEPROM Enable LOW input enables EEPROM access.

0=enable EEPROM use

1=connect to logic 1 state

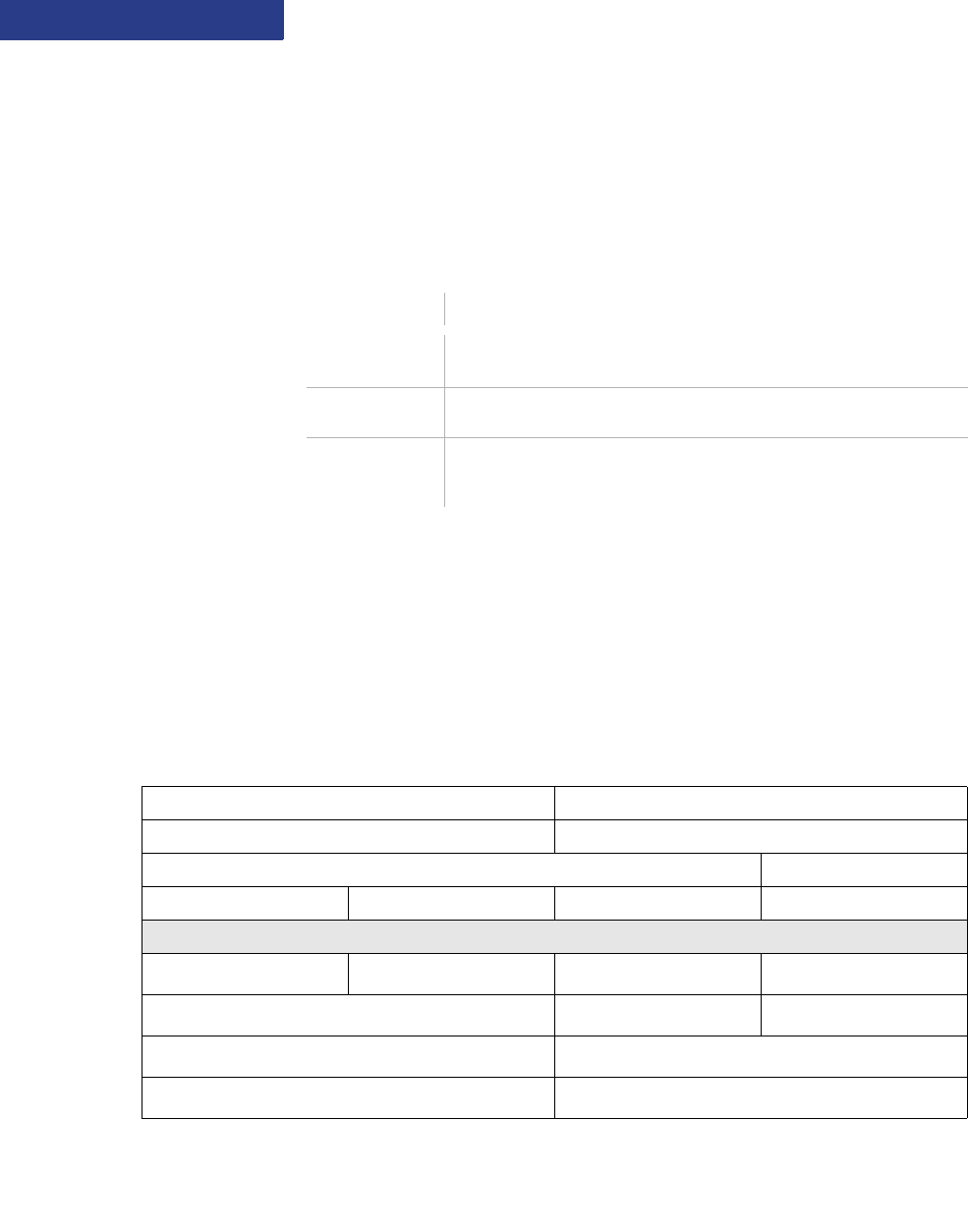

Primary

Offset 31 24 23 16 15 8 7 0

00h Device ID Vendor ID

04h Primary Status Primary Command

08h Class Code Revision ID

0Ch BIST Header Type Primary Latency Time Cache Line Size

10h

reserved

18h Secondary Latency Timer

Subordinate Bus Number Secondary Bus Number Primary Bus Number

1Ch

Secondary Status I/O Limit I/O Base

20h

Memory Limit Memory Base

24h

Prefetchable Memory Limit Prefetchable Memory Base

Ta b l e 3 - 6 :

PLX PCI 6254 Configuration

Signals

R e g i s t e r 3 - 2 :

PCI6254 Configuration Registers–

Transparent Mode