Electrical Specifications

138 Intel® Xeon® Processor E5-1600 v2/E5-2600 v2 Product Families

Datasheet Volume One of Two

7.3 Power-On Configuration (POC) Options

Several configuration options can be configured by hardware. The processor samples

its hardware configuration at reset, on the active-to-inactive transition of RESET_N, or

upon assertion of PWRGOOD (inactive-to-active transition). For specifics on these

options, please refer to Table 7-7.

The sampled information configures the processor for subsequent operation. These

configuration options cannot be changed except by another reset transition of the

latching signal (RESET_N or PWRGOOD).

Notes:

1. Output tri-state option enables Fault Resilient Booting (FRB), for FRB details see Section 7.4. The signal

used to latch PROCHOT_N for enabling FRB mode is RESET_N.

2. BIST_ENABLE is sampled at RESET_N de-assertion (on the falling edge).

3. This signal is sampled after PWRGOOD assertion.

7.4 Fault Resilient Booting (FRB)

The processor supports both socket and core level Fault Resilient Booting (FRB), which

provides the ability to boot the system as long as there is one processor functional in

the system. One limitation to socket level FRB is that the system cannot boot if the

legacy socket that connects to an active PCH becomes unavailable since this is the path

to the system BIOS. See Table 7-8 for a list of output tri-state FRB signals.

Socket level FRB will tri-state processor outputs via the PROCHOT_N signal. Assertion

of the PROCHOT_N signal through RESET_N de-assertion will tri-state processor

outputs. Note, that individual core disabling is also supported for those cases where

disabling the entire package is not desired.

The processor extends the FRB capability to the core granularity by maintaining a

register in the uncore so that BIOS or another entity can disable one or more specific

processor cores.

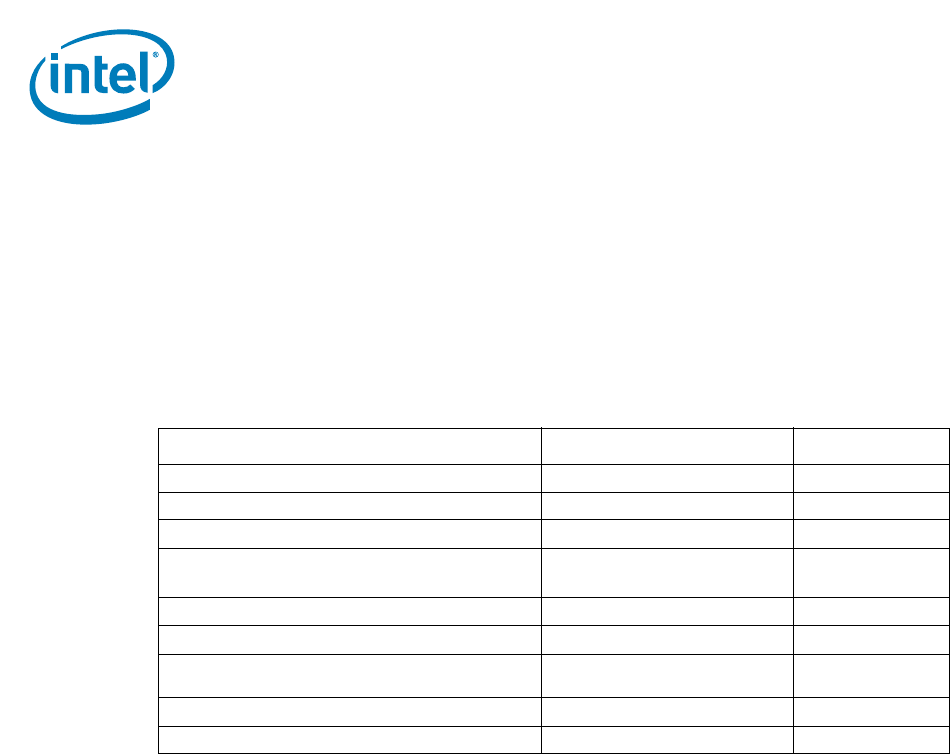

Table 7-7. Power-On Configuration Option Lands

Configuration Option Land Name Notes

Output tri state PROCHOT_N 1

Execute BIST (Built-In Self Test) BIST_ENABLE 2

Enable Service Processor Boot Mode BMCINIT 3

Enable Intel® Trusted Execution Technology (Intel®

TXT) Platform

TXT_PLTEN

3

Power-up Sequence Halt for ITP configuration EAR_N 3

Enable Bootable Firmware Agent FRMAGENT 3

Enable Intel Trusted Execution Technology

(Intel TXT) Agent

TXT_AGENT

3

Enable Safe Mode Boot SAFE_MODE_BOOT 3

Configure Socket ID SOCKET_ID[1:0] 3