Overview

Intel® Xeon® Processor E5-1600 v2/E5-2600 v2 Product Families 17

Datasheet Volume One of Two

• Power Management Event (PME) functions.

• Message Signaled Interrupt (MSI and MSI-X) messages

• Degraded Mode support and Lane Reversal support

• Static lane numbering reversal and polarity inversion support

• Support for PCIe* 3.0 atomic operation, PCIe 3.0 optional extension on atomic

read-modify-write mechanism

• Additional read buffers for point-point transfers. This increases the number of

outstanding transactions in point-point transfers across same processor sockets,

from previous generation of 16 to 64 in this generation.

1.2.3 Direct Media Interface Gen 2 (DMI2)

• Serves as the chip-to-chip interface to the Intel® C600 Chipset

• The DMI2 port supports x4 link width and only operates in a x4 mode when in DMI2

• Operates at PCI Express* 1.0 or 2.0 speeds

• Transparent to software

• Processor and peer-to-peer writes and reads with 64-bit address support

• APIC and Message Signaled Interrupt (MSI) support. Will send Intel-defined “End of

Interrupt” broadcast message when initiated by the processor.

• Downstream System Management Interrupt (SMI), SCI, and SERR error indication

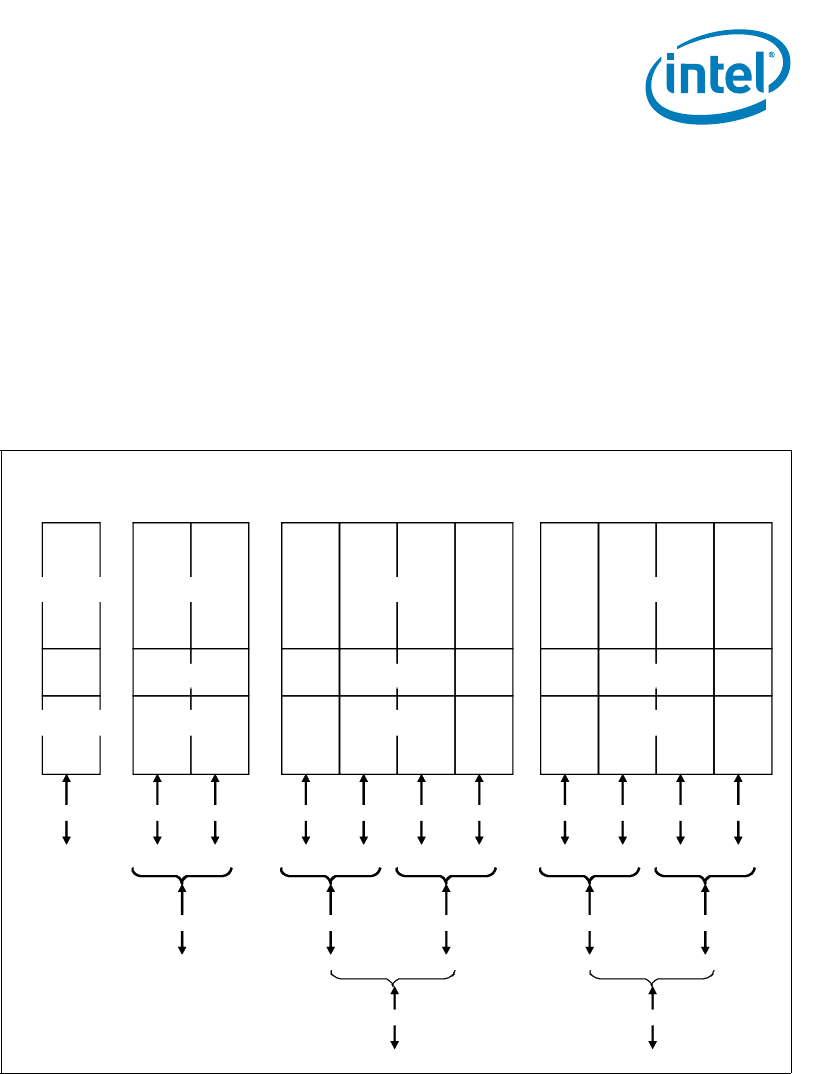

Figure 1-3. PCI Express* Lane Partitioning and Direct Media Interface Gen 2 (DMI2)

Transaction

Link

Physical

0…3

X4

DMI

Port 0

DMI / PCIe

4…7

X4

Port 1b

Transaction

Link

Physical

0…3

X4

Port 1a

Port 1

(IOU2)

PCIe

X8

Port 1a

8…11

Transaction

Link

Physical

0…3

Port 2

(IOU0)

PCIe

X4

Port 2b

X4

Port 2a

X8

Port 2a

X4

Port 2d

X4

Port 2c

X8

Port 2c

X16

Port 2a

12..154…7 8…11

Transaction

Link

Physical

0…3

Port 3

(IOU1)

PCIe

X4

Port 3b

X4

Port 3a

X8

Port 3a

X4

Port 3d

X4

Port 3c

X8

Port 3c

X16

Port 3a

12..154…7