Intel® Xeon® Processor E5-1600 v2/E5-2600 v2 Product Families 45

Datasheet Volume One of Two

Interfaces

2.5.2.6.10 DRAM Power Limit Performance Status Read

This service allows the PECI host to assess the performance impact of the currently

active DRAM power limiting modes. The read return data contains the sum of all the

time durations for which each of the DIMMs has been operating in a low power state.

This information is tracked by a 32-bit counter that wraps around. The unit for time is

determined as per the Package Power SKU Unit settings described in

Section 2.5.2.6.11. The DRAM performance data does not account for stalls on the

memory interface.

In general, for the purposes of DRAM RAPL, the DRAM power management entity

should use PECI accesses to DRAM energy and performance status in conjunction with

the power limiting feature to budget power between the various memory sub-systems

in the server system.

2.5.2.6.11 CPU Thermal and Power Optimization Capabilities

Table 2-8 provides a summary of the processor power and thermal optimization

capabilities that can be accessed over PECI.

Note: The Index values referenced in Table 2-8 are in decimal format.

Table 2-8 also provides information on alternate inband mechanisms to access similar

or equivalent information for register reads and writes where applicable. The user

should consult the appropriate Intel® Xeon® Processor E5 v2 Product Family Processor

Datasheet, Volume Two: Registers for exact details on MSR or CSR register content.

Figure 2-19. DRAM Power Limit Data

DRAM_POWER_LIMIT Data

DRAM

Power Limit

Enable

1523

DRAM Power Limit

14 0

RESERVED

16

Control Time

Window

1731

RESERVED

24

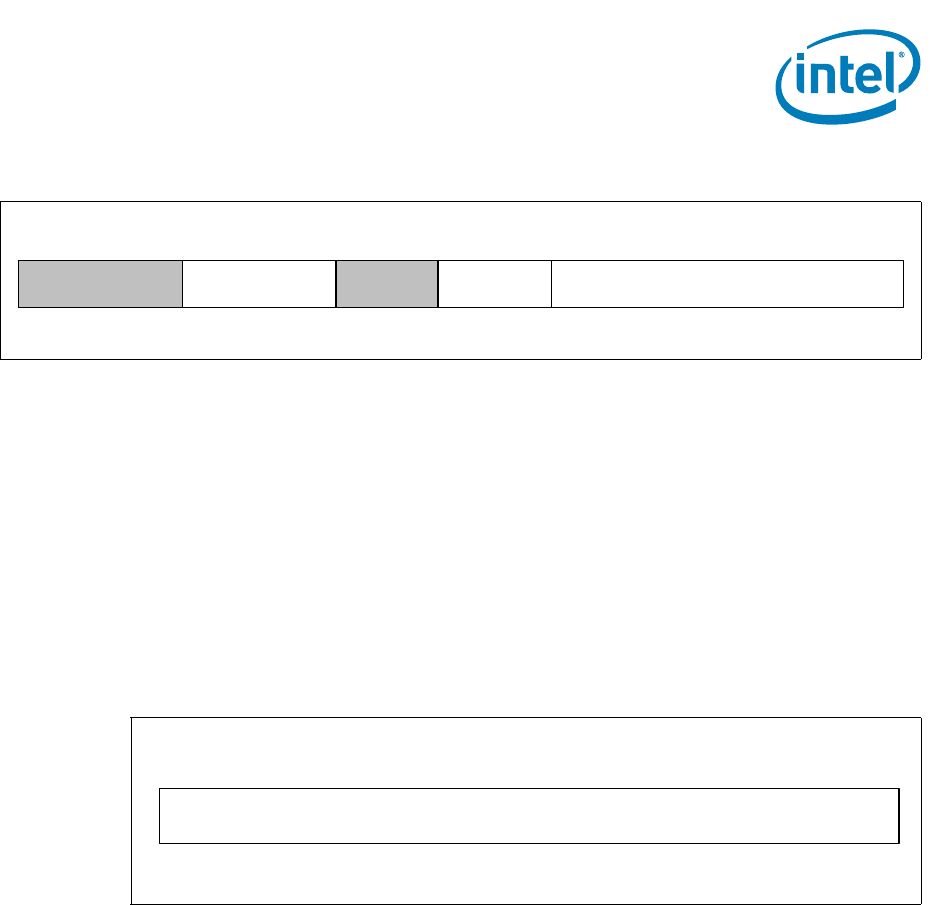

Figure 2-20. DRAM Power Limit Performance Data

DRAM Power Limit Performance

Accumulated DRAM Throttle Time

0

31