Intel® Xeon® Processor E5-1600 v2/E5-2600 v2 Product Families 89

Datasheet Volume One of Two

Power Management

While individual threads can request low power C-states, power saving actions only

take place once the core C-state is resolved. Core C-states are automatically resolved

by the processor. For thread and core C-states, a transition to and from C0 is required

before entering any other C-state.

4.2.3 Requesting Low-Power Idle States

The core C-state will be C1E if all actives cores have also resolved a core C1 state or

higher.

The primary software interfaces for requesting low power idle states are through the

MWAIT instruction with sub-state hints and the HLT instruction (for C1 and C1E).

However, software may make C-state requests using the legacy method of I/O reads

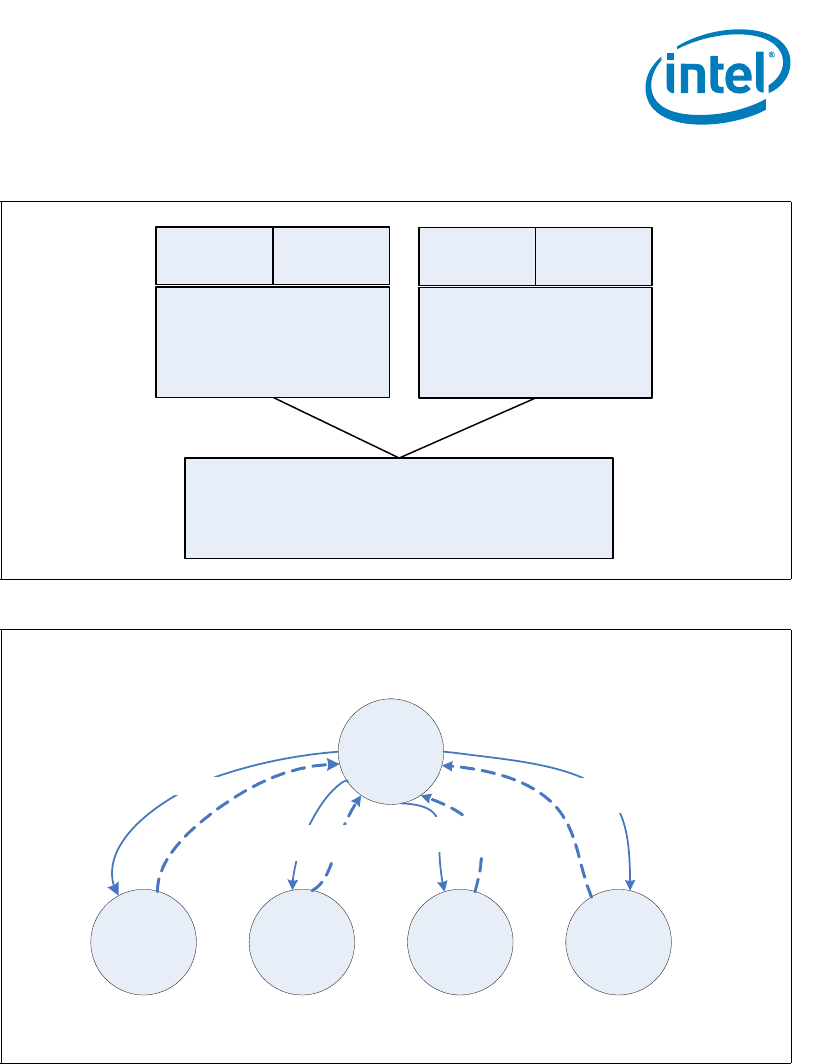

Figure 4-1. Idle Power Management Breakdown of the Processor Cores

Figure 4-2. Thread and Core C-State Entry and Exit

Processor Package State

Core N State

Thread 1Thread 0

Core 0 State

Thread 1Thread 0

C1 C1E C6C3

MWAIT(C1), HLT

C0

MWAIT(C6),

P_LVL3 I/O Read

MWAIT(C3),

P_LVL2 I/O Read

MWAIT(C1), HLT

(C1E Enabled)