104 Datasheet

Signals Reference

A.1.59 STBn[7:0]# and STBp[7:0]# (I/O)

STBp[7:0]# and STBn[7:0]# (and DRDY#) are used to transfer data at the 2x transfer rate in lieu of

BCLKp. They are driven by the data transfer agent with a tight skew relationship with respect to its

corresponding bus signals, and are used by the receiving agent to capture valid data in its latches.

This functions like an independent double frequency clock constructed from a falling edge of either

STBp[7:0]# or STBn[7:0]#. The data is synchronized by DRDY#. Each strobe pair is associated

with 16 data bus signals and two ECC signals as shown in Table A-11.

A.1.60 TCK (I)

The Test Clock (TCK) signal provides the clock input for the IEEE 1149.1 compliant TAP.

A.1.61 TDI (I)

The Test Data In (TDI) signal transfers serial test data into the Itanium 2 processor. TDI provides

the serial input needed for IEEE 1149.1 compliant TAP.

A.1.62 TDO (O)

The Test Data Out (TDO) signal transfers serial test data out from the Itanium 2 processor. TDO

provides the serial output needed for IEEE 1149.1 compliant TAP.

A.1.63 THRMTRIP# (O)

The Thermal Trip (THRMTRIP#) signal protects the Itanium 2 processor from catastrophic

overheating by use of an internal thermal sensor. This sensor is set well above the normal operating

temperature to ensure that there are no false trips. Data will be lost if the processor goes into

thermal trip (signaled to the system by the assertion of the THRMTRIP# signal). Once

THRMTRIP# is asserted, the platform must assert RESET# to protect the physical integrity of the

processor.

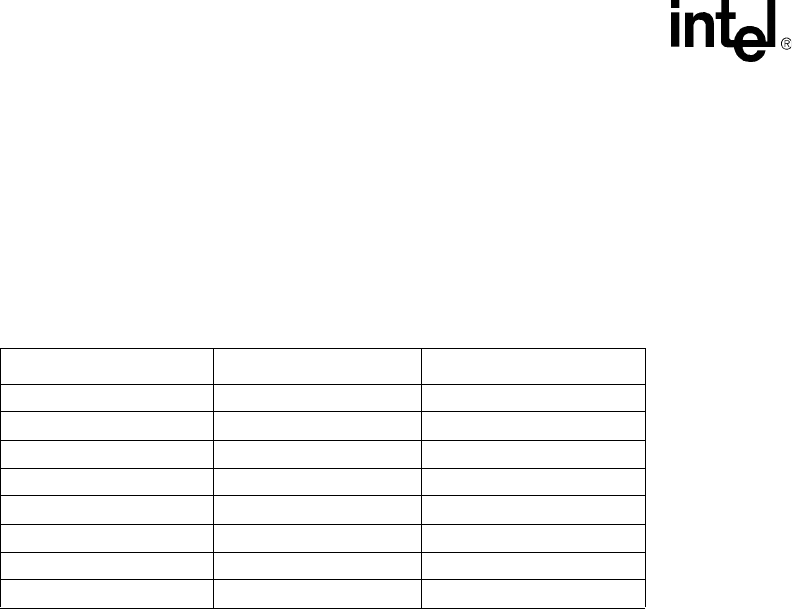

Table A-11. STBp[7:0]# and STBn[7:0]# Associations

Strobe Bits Data Bits ECC Bits

STBp[7]#, STBn[7]# D[127:112]# DEP[15:14]#

STBp[6]#, STBn[6]# D[111:96]# DEP[13:12]#

STBp[5]#, STBn[5]# D[95:80]# DEP[11:10]#

STBp[4]#, STBn[4]# D[79:64]# DEP[9:8]#

STBp[3]#, STBn[3]# D[63:48]# DEP[7:6]#

STBp[2]#, STBn[2]# D[47:32]# DEP[5:4]#

STBp[1]#, STBn[1]# D[31:16]# DEP[3:2]#

STBp[0]#, STBn[0]# D[15:0]# DEP[1:0]#