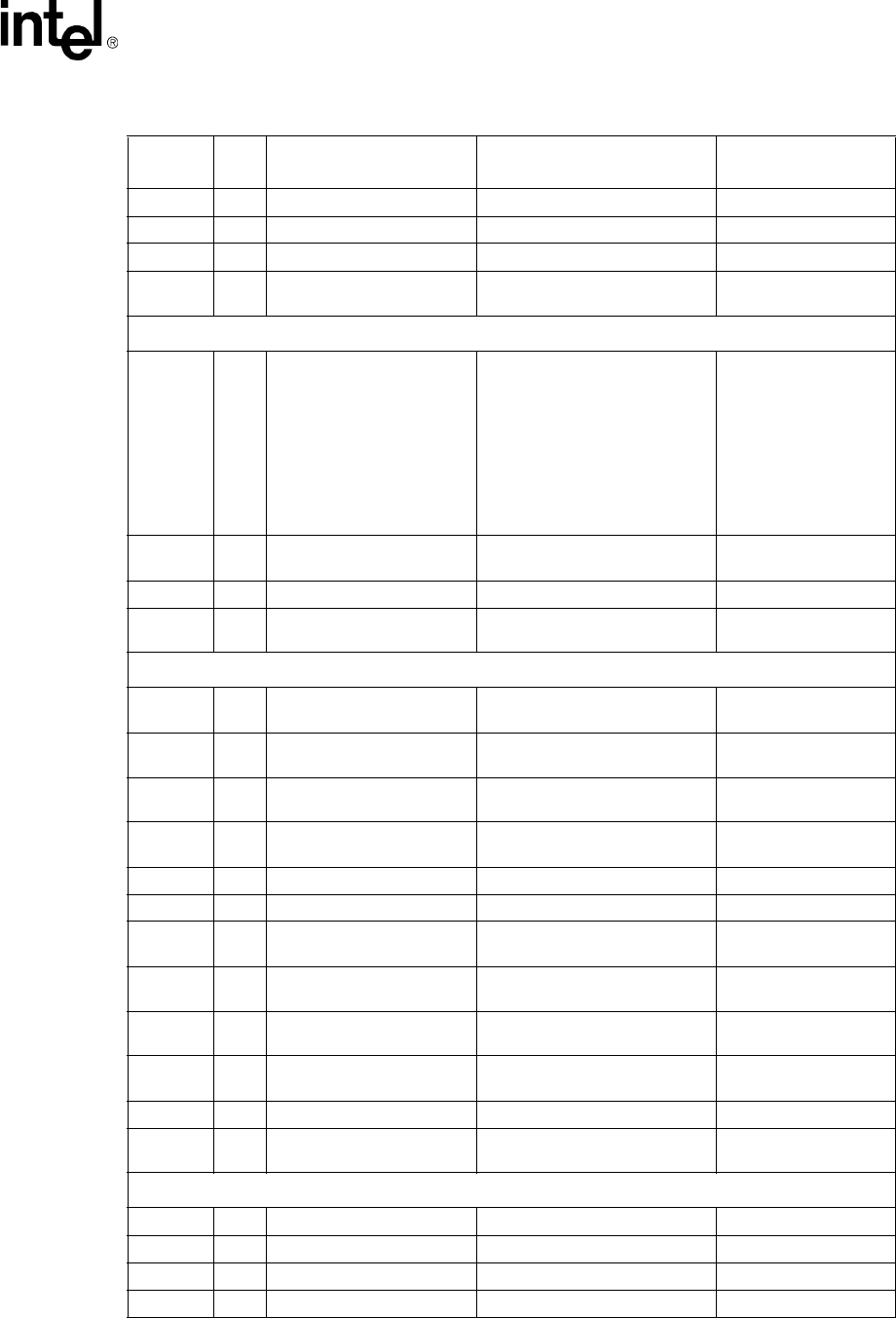

Datasheet 83

System Management Feature Specifications

09h 8 Feature Data Address Byte pointer, 00h if not present 67h

0Ah 8 Other Data Address Byte pointer, 00h if not present 7Ah

0Bh 16 Reserved Reserved for future use 0000h

0Dh 8 Checksum 1 byte checksum Add up by byte and

take 2’s complement.

Processor

0Eh 48 S-spec Number Six 8-bit ASCII characters S-spec number of S123

would be:

• 13h = 00h

• 12h = 00h

• 11h = “3”

• 10h = “2”

•0Fh = “1”

•0Eh = “S”

14h 2 Sample/Production 00b = Sample only (MSB First) 00000001b =

Production

15h 8 Reserved Reserved for future use 00h

16h 8 Checksum 1 byte checksum Add up by byte and

take 2’s complement.

Core

17h 8 Architecture Revision From CPUID

1

Taken from

CPUID[3].archrev.

18h 8 Processor Core Family From CPUID Taken from

CPUID[3].family.

19h 8 Processor Core Model From CPUID Taken from

CPUID[3].model.

1Ah 8 Processor Core Stepping From CPUID Taken from

CPUID[3].revision.

1Bh 24 Reserved Reserved for future use 000000h

1Eh 16 Maximum Core Frequency Four 4-bit hex digits (in MHz) 1 GHz = 1000h

2

20h 12 Maximum System Bus

Frequency

Three 4-bit hex digits (in MHz) 200 MHz = 200h

1

22h 16 Core Voltage ID Voltage in four 4-bit hex digits

(in mV)

1500 mV = 1500h

1

24h 8 Core Voltage Tolerance,

High

Edge finger tolerance in mV, +

two 4-bit hex digits

1.5% = 22 mV = 22h

1

25h 8 Core Voltage Tolerance,

Low

Edge finger tolerance in mV, –

two 4-bit hex digits

1.5% = 22 mV = 22h

1

26h 8 Reserved Reserved for future use 00h

27h 8 Checksum 1 byte checksum Add up by byte and

take 2’s complement.

Cache

28h 32 Reserved Reserved for future use 00000000h

2Ch 16 Cache Size Four 4-bit hex digits (in Kbytes) 3072 Kbytes = 3072h

1

2Eh 64 Reserved Reserved for future use x0h

36h 8 Checksum 1 byte checksum

Table 6-4. Processor Information ROM Format (Sheet 2 of 4)

Offset/

Section

# of

Bits

Function Notes Examples