Datasheet 81

System Management Feature Specifications

6.1.3 SMBus Device Addressing

Of the addresses broadcast across the SMBus, the memory components claim those of the form

“1010XXYZb”. The “XX” and “Y” bits are used to enable the devices on the processor at adjacent

addresses. The Y bit is hard-wired on the processor to GND (‘0’) for the Scratch EEPROM and

pulled to 3.3V (‘1’) for the processor information ROM. The “XX” bits are defined by the

processor socket via the SMA0 and SMA1 pins on the Itanium 2 processor connector. These

address pins have a weak pull-down (10 kΩ) to ensure that the memory components are in a known

state in systems which do not support the SMBus, or only support a partial implementation. The

“Z” bit is the read/write bit for the serial bus transaction.

The thermal sensing device internally decodes 1 of 3 upper address patterns from the bus of the

form “0011XXXZb”, “1001XXXZb” or “0101XXXZb”. The device’s addressing, as implemented,

uses SMA2 and SMA1 and includes a Hi-Z state for the SMA2 address pin. Therefore, the thermal

sensing device supports six unique resulting addresses. To set the Hi-Z state for SMA2, the pin

must be left floating. The system should drive SMA1 and SMA0, and will be pulled low (if not

driven) by the 10 kΩ pull-down resistor on the processor substrate. Attempting to drive either of

these signals to a Hi-Z state would cause ambiguity in the memory device address decode, possibly

resulting in the devices not responding, thus timing out or hanging the SMBus. As before, the “Z”

bit is the read/write bit for the serial bus transaction.

Figure 6-1 shows a logical diagram of the pin connections. Table 6-2 and Table 6-3 describe the

address pin connections and how they affect the addressing of the devices.

Note: Addresses of the form “0000XXXXb” are Reserved and should not be generated by an SMBus

master. Also, system management software must be aware of the processor select in the address for

the thermal sensing device.

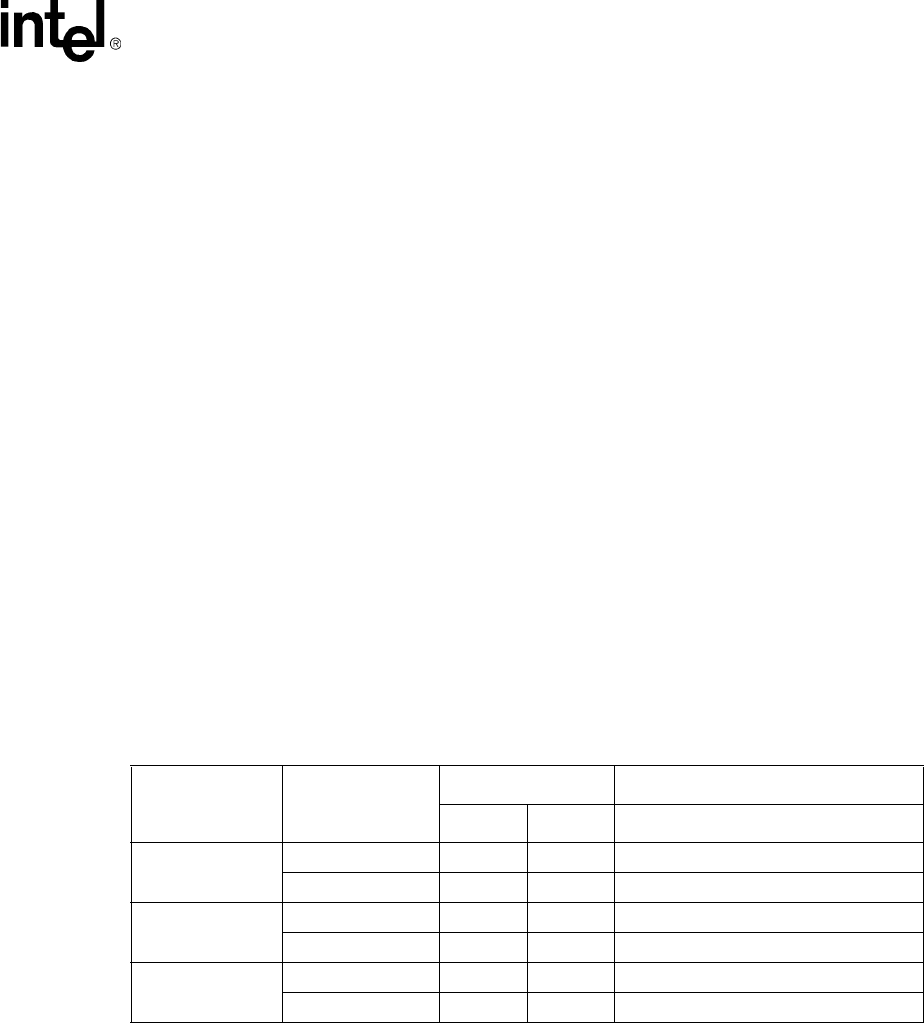

Table 6-2. Thermal Sensing Device SMBus Addressing on the Itanium

®

2 Processor

Address (Hex) Upper Address

1

NOTES:

1. Upper address bits are decoded in conjunction with the select pins.

Processor Select 8-Bit Address Word on Serial Bus

SMA2 SMA1 b[7:0]

3Xh 0011 0 0 0011000Xb

0011 0 1 0011010Xb

5Xh 0101 Z

2

2. A tri-state or “Z” state on this pin is achieved by leaving this pin unconnected.

0 0101001Xb

0101 Z

b

1 0101011Xb

9Xh 1001 1 0 1001100Xb

1001 1 1 1001110Xb