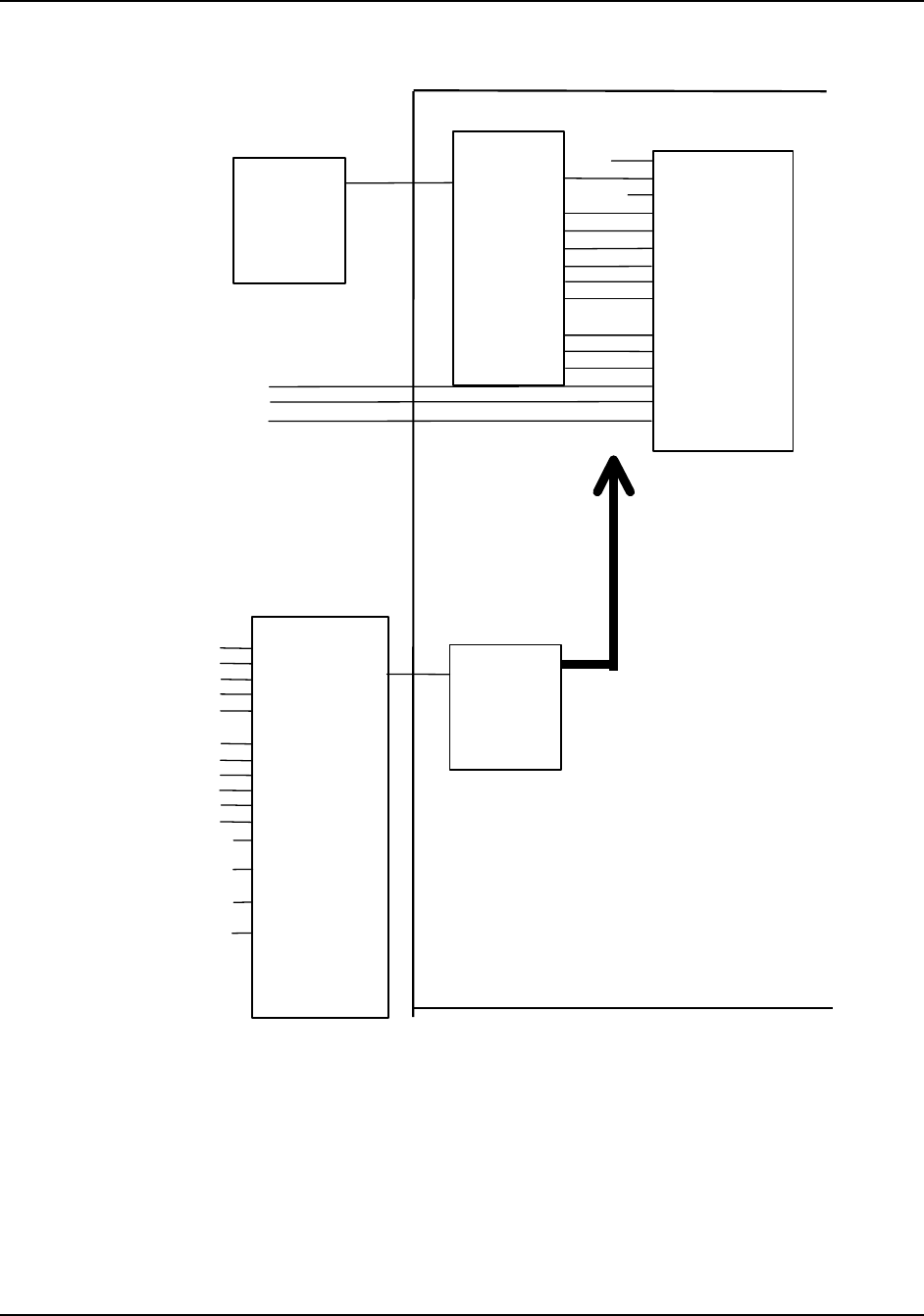

Baseboard PCI I/O Subsystem Intel® SHG2 DP Server Board Technical Product Specification

Intel Order Number C11343-001 Revision 1.0

24

CSB5

SCSI

i

INTB#

j

S

lot1intB,Slot2intD,Slot3intC,

S

lot4intD,Slot5intC,Slot6intB

1

s

t

LAN 82550

Slot3 intA

Slot6 intA

Slot4 intA

Slot2 intA

SCSI

i

INTA#

j

IRQ 0

IRQ 1

IRQ 2

IRQ 3

IRQ 4

IRQ 5

IRQ 6

IRQ 7

IRQ #8

IRQ 9

IRQ 10

IRQ 11

IRQ 12

IRQ 13

IRQ 14

IRQ 15

Timer

Cascade

Connection

Map PCI IRQ to

IRQ[1,3:7, 9:12, 14,15]

SCAN PIRQ

PIRQ 0

PIRQ 1

PIRQ 2

PIRQ 3

PIRQ 4

PIRQ 5

PIRQ 6

PIRQ 7

PIRQ 8

PIRQ 9

PIRQ 10

PIRQ 11

PIRQ12

PIRQ13

PIRQ14

PIRQ 15

PCI Interrupts Address Index Register

PCI Interrupt Redirection Register

IO Address(c00h)

IO Address(c01h)

SCAN IRQ

Keyboard

Serial Port2

Serial Port1

ESMINT

FDD

Parallel Port

RTC

ESMINT

ESMINT

Mouse

FERR#

Super I/O

Slot1 intA

2

n

d

LAN 82544

GA

Slot5 intA

SCI

S

lot1intD,Slot2intC,Slot3intB,

S

lot4intC,Slot5intB

S

lot1intC,Slot2intB,Slot3intD,

S

lot4intB,Slot5intD

PCI

Interrupt

Router

P_IDE

S_IDE

Figure 4. SHG2 Interrupt Routing (PIC Mode)