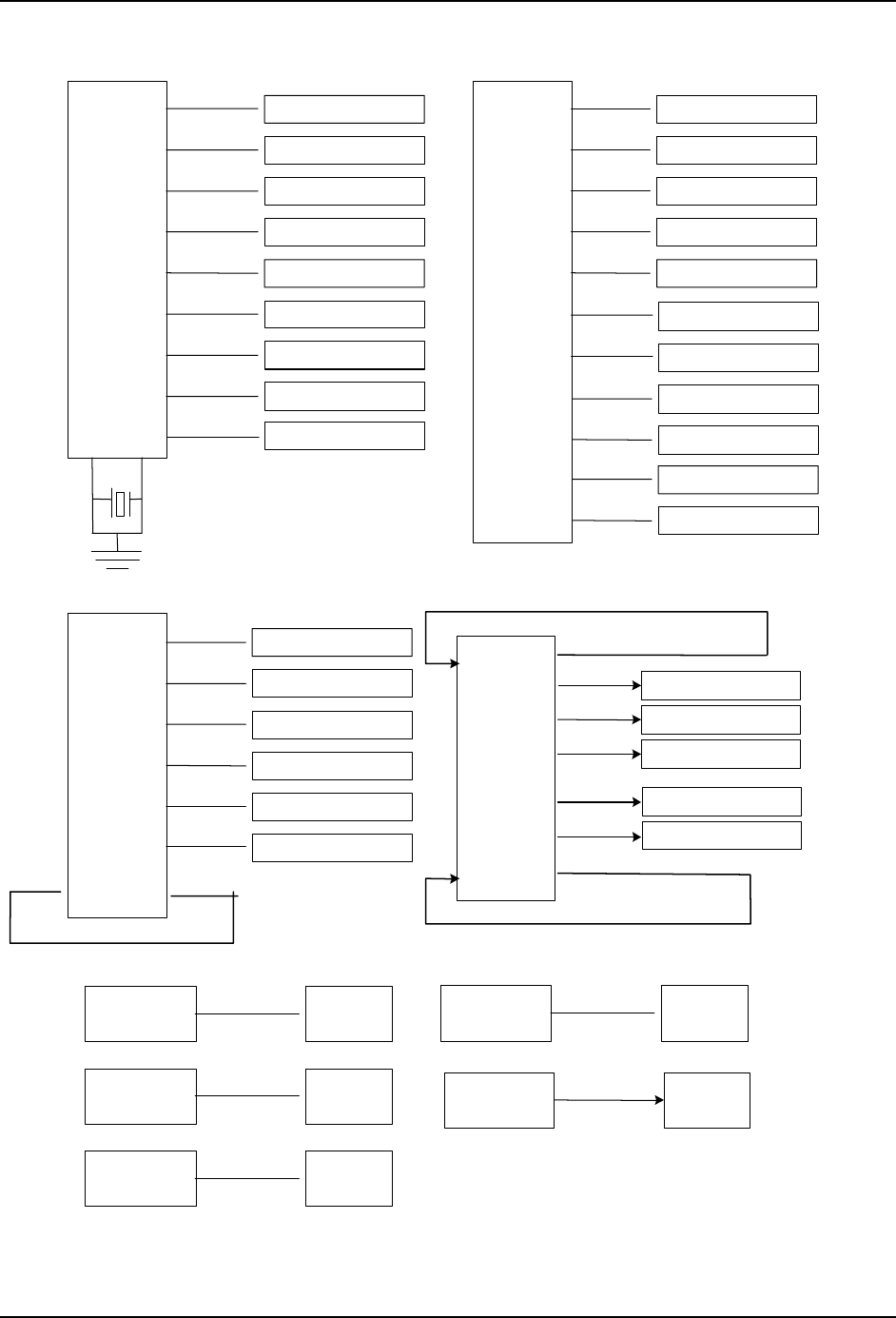

Clock Generation and Distribution Intel® SHG2 DP Server Board Technical Product Specification

Intel Order Number C11343-001 Revision 1.0

28

CIOB-X2

Primary

Secondary

Osc

40 MHz

Crystal

32.768 MHz

Crystal

25 MHz

Crystal

32.768 MHz

A

IC

7899

SIO

82550

BMC

I/O CLOCK:

OTHER CLOCKS:

PCI

CLOCK

BUFFER

BMC

NIC 82550PM

VG

A

SIO

33 MHz

33 MHz

33 MHz

33 MHz

PCI Slot #3

IRQ #1

IR1 #0

33 MHz

33 MHz

33 MHz

33 MHz

PCI CLOCK:

PCI Slot #4

33 MHz

PCI Slot #5

CSB5

CIOB-X2

33 MHz

33 MHz

HOST

CLOCK

BUFFER

14.318MHz

CPU1

CPU2

CMIC-LE

MEM CLK BUF

100 MHz

100 MHz

100 MHz

100 MHz

ITP

CSB5 / VGA

SIO

CSB5 / SIO

100 MHz

14 MHz

48 MHz

48 MHz

HOST CLOCK:

PCI CLK BUF

33 MHz

MEM

CLOCK

BUFFER

DIMM SLOT A1

DIMM SLOT B1

DIMM SLOT A2

DIMM SLOT B2

100 MHz

100 MHz

100 MHz

100 MHz

DIMM SLOT A3

DIMM SLOT B3

100 MHz

100 MHz

100 MHz

MEM CLOCK:

100 MHz

PCI-X Slot #1

PCI-X Slot #2

NIC 82544GC

100 MHz

100 MHz

100 MHz

PCI-X Slot #6

ULTRA 160

66/133 MHz

66/133 MHz

66/133 MHz

Crystal

40 MHz

BMC

Figure 6. SHG2 Baseboard Clock Distribution