Error Reporting and Handling Intel® SHG2 DP Server Board Technical Product Specification

Intel Order Number C11343-001 Revision 1.0

40

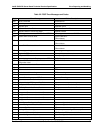

6.5.1 Alert Standard Forum (ASF) Progress Codes

The BIOS utilizes ASF Progress Events as described in the ASF Specification, Revision 1.0a

from the Distributed Management Task Force (DMTF). BIOS supported events are shown in

Table 28.

Table 28. Event Request Message Event Data Field Contents

ASF Code Description Comment

01h Memory initialization. At beginning of ECC initialization or memory test.

02h Hard-disk initialization At beginning of IDE device detection.

03h Secondary processor(s) initialization At beginning of MP Init

04h User authentication When waiting for User/Supervisor password

05h User-initiated system setup When Setup is invoked

06h USB resource configuration When USB devices scan/initialization begins

07h PCI resource configuration At beginning of configuring PCI devices in system.

08h Option ROM initialization At beginning of Option ROM scan

09h Video initialization At beginning of initialization primary video controller (if

present)

0Ah Cache initialization At beginning of setting up processor cache

0Bh SM Bus initialization At beginning of configuring SMBus to communicate

with BMC

0Ch Keyboard controller initialization At keyboard discovery scan

0Dh Embedded controller/management

controller initialization

When first checking for functional BMC

12h Calling operating system wake-up

vector

When waking from Wake-On-LAN, Wake-On-Ring,

Magic Packet, etc.

13h Starting operating system boot

process, e.g. calling Int 19h

Immediately prior to calling INT19h

6.5.2 Power-On Self Test (POST) Codes

The BIOS indicates the current testing phase to I/O location 80h and to the LCD on the front

panel during POST after the video adapter has been successfully initialized. If a Port-80h card

(Postcard*) is installed, it displays this 2-digit code on a pair of hex display LEDs.

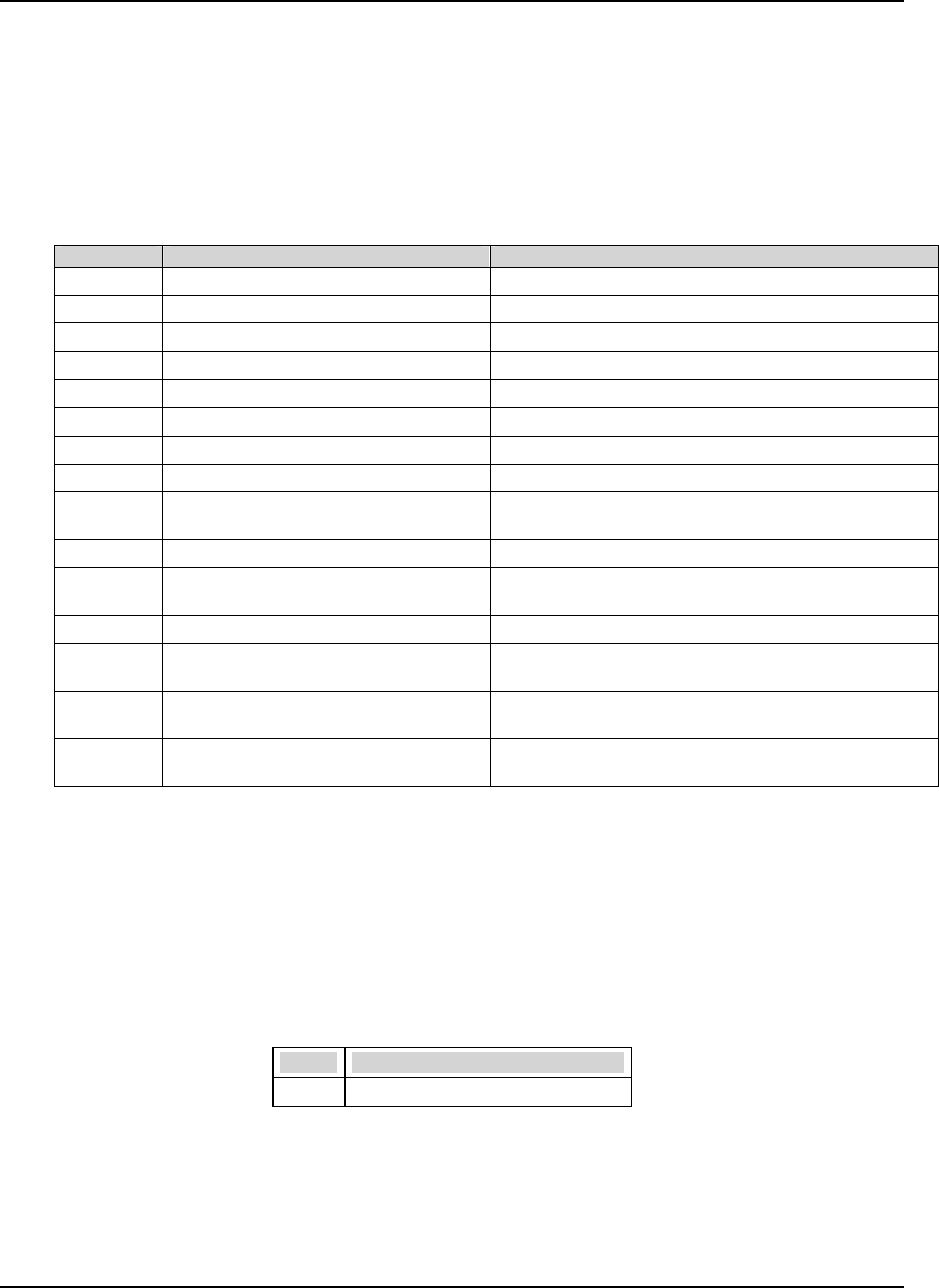

Table 29. Port-80h Code Definition

Code Meaning

CP Phoenix* check point POST code

Table 30 contains the POST codes displayed during the boot process. A beep code is a series

of individual beeps on the PC speaker, each of equal length. This table describes the error

conditions associated with each beep code and the corresponding POST checks point code as

seen by a ‘port 80h’ card and LCD. For example, if an error occurs at checkpoint 22h, a beep